您好!

在我的项目中、我使用分配给3个 UART TX 通道的3个 DMA 通道。 其余的 DMA 通道应该未使用。 我要求确保寄存器写入、并且我按以下方式执行:

空 WriteAndRead (volatile uint32_t*常量 preg,常量 uint32_t 值)

{

*preg=(uint32_t)值);

Volatile uint32_t actualValue =*半固化;

if ((actualValue & value)!= value)

{

ErrorRaise (值、实际值、*半固化片、半固化片)

}

}

借助上述代码、我能够用 非常罕见的发生率 例如调用参数(uint32_t*) 0xFFf80030、0xe)和以下错误参数:

1:0xe、

2:0x0、

3:0xe、

4:0xFFF80030

因此、直到到控制数据包 RAM 的写入完成并且第一次读取操作(param 2)没有返回一个预期值、CPU 似乎没有被阻止。 但在几个时钟周期后、可以观察到正确的值(第3段)。

在《技术参考手册》SPNU563A 中、我找到了以下信息

"20.3.2通道配置":

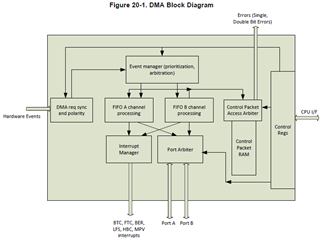

"- RAM 可由队列 A 和队列 B 状态机以及 CPU 访问。"

"-当有同时访问时、优先级在一个固定优先级机制中由 CPU 解析

具有最高优先级。"

我的问题是:

-这是写或读操作的问题吗? 我需要确保在 DMA 传输触发之前所有参数都到位。

-我们是否可以估计需要应用的最大延迟值,以确保数据到位?

-如果应用一些 do-while ()循环修复一个问题,或者只是隐藏它? 能否说明此类行为的一些背景?

-从参考手册看,软件访问应该具有最高优先级,所以我不明白为什么这个问题是可见的。

感谢您的帮助、

此致、

S·索科洛夫斯基