主题中讨论的其他器件: UNIFLASH、 SysConfig

您好、

我对 AM2434 GP EVM 上的闪存驱动器设置有疑问。

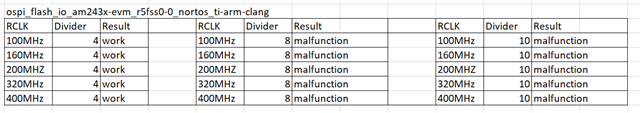

1.运行 ospi_flash_diag 演示工程、从默认闪存 S28HS512T 获取 SFDP 数据。 然后、我为 S28HS512T 创建 json 文件、

e2e.ti.com/.../s28hs512t.txte2e.ti.com/.../s28hs512t.json

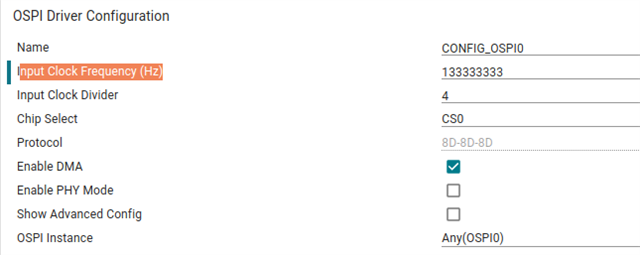

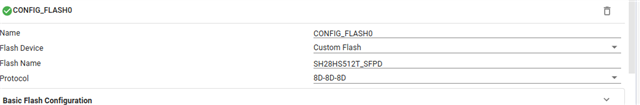

2.在 sbl_uart_uniflash 项目中,我创建新的自定义配置

加载我以前获取的 json 文件。 (我使用 syscfg-tool 1.16、而不是默认1.14、因为1.4出现问题)

3.重新编译它并将其用作新的闪存写入器。 对默认 SBL_null 映像进行编程。

但是、新的 SBL_UART_uniflash 映像不起作用。

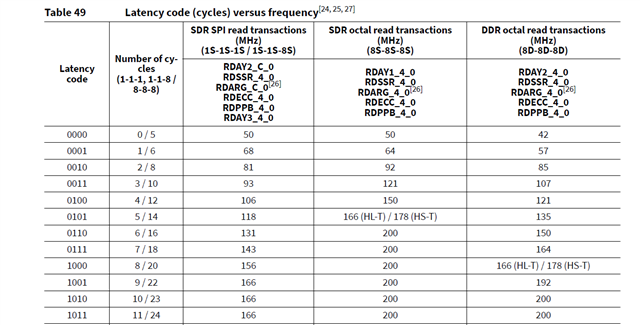

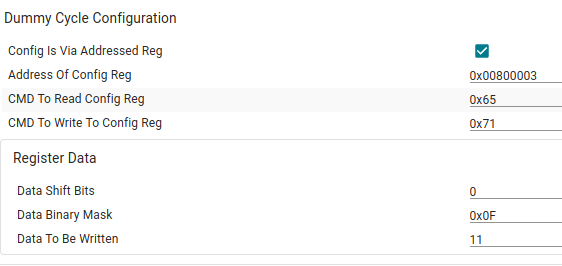

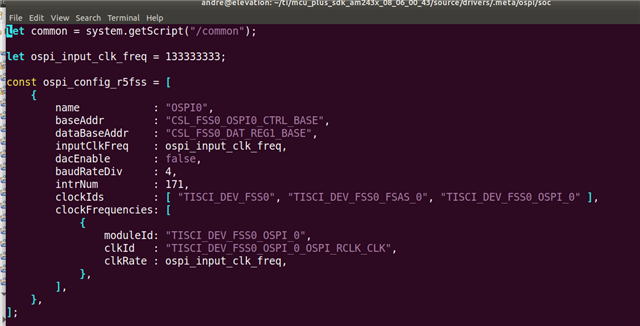

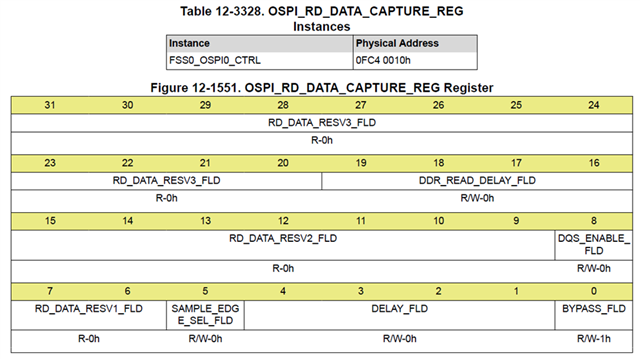

4.我比较了默认闪存驱动器设置和从 json 文件加载之间的差异。 我发现多项设置不同。

我在这里强调一下:

虚拟周期设置、协议启用配置设置和寄存器位/位掩码在默认情况下是不同的。

4.我改回默认设置,重新编译,然后一切顺利。

在这里提问。

1.为什么默认设置要比 SFPD 表中得到的结果差? 哪一个与闪存数据表中的描述匹配?

2.自动从"加载 SFPD" json 文件生成的 syscfg 不起作用?

此致

安德烈