请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:TLV320AIC23B 您好,

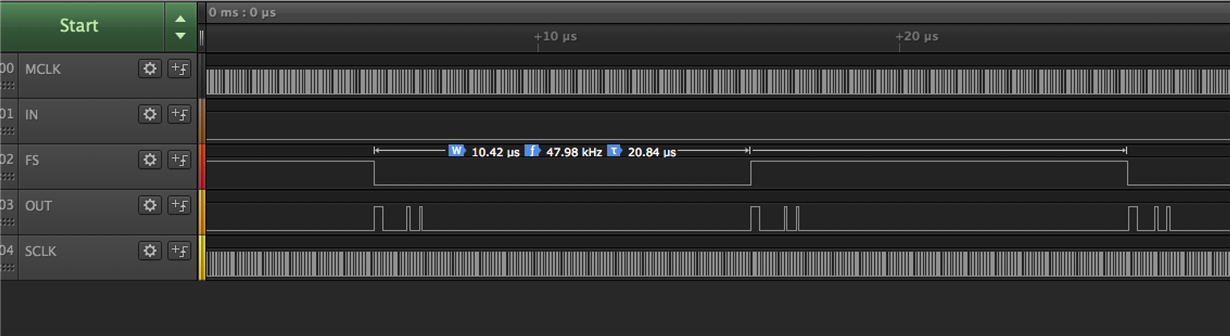

我有一个 µController连接到 TLV320AIC23B,以便适配包含立体声耳机和麦克风的耳机。 我已成功将设备配置为播放400Hz窦性波。 我将该信号反馈给麦克风输入,但我看不到任何数字输出。 我可以利用一些帮助来找出我在这里做错了什么。

解码器被配置为从属。 主时钟(MCLK )由 µController驱动,设置为12MHz,位时钟(BLCK)设置为3MHz。 LRCIN为48kHz。 我可以测量 MICP引脚处140mV RMS的400Hz信号。 MICBIAS在~2.5V DC下。

设备按照以下顺序进行配置。 这是使用I2C接口写入器件的字节序列:

0x1E,0x00

将0x00写入重置寄存器(0x0F)应会导致设备重置

0x08,0x14

将0x14写入 模拟音频路径控制(0x04)应选择麦克风作为ADC (Insel)的输入,并将DAC (DAC)侧音的输出设置为禁用。 无旁路,麦克风未增强。

0x0A,0x00

将0x00写入 数字音频路径控制(0x05)应禁用 DAC软静音(DACM)

0x10,0x01

将0x01写入 采样率控制寄存器(0x08)应禁用所有时钟分配器,并根据3.3 模式下的.2.1 表中的第3行将采样率配置为48kHz

0x0C,0x21

将0x21写入断电控制寄存器(0x06)应关闭振荡器(OSC)和线路输入(line)。

0x0E,0x01

将0x01写入数字音频接口格式寄存器(0x07)应将设备配置为从属设备(MS=0),将输入长度设置为16位(WL[1:0]=0,0), 数据格式首先是MSB,左对齐(for [1:0]=0,1)

0x12,0x01

将0x01写入 数字接口激活寄存器(0x09)应激活数字接口(Act)。

0x05,0x7f

将0x17f写入 左声道耳机音量控制寄存器(0x01)应同时将左声道和右声道(LRS)的音量值更新为+6 dB (LHV[6:0]=11.1111万11111)</s>1.1111万

0x01,0x18

将0x118写入 左线路输入通道音量控制寄存器(0x00) 应同时将左侧和右侧通道(LRS)线路输入音量更新为1.5 db (LIV[4:0]=1.1万)

结果是,我在DOUT引脚上看不到任何高级值。 我在这里做错了吗?

提前感谢大家花时间来了解这一情况。 我们高度赞赏每一条评论,想法或指针。

此致,

Torsten