https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1045180/tlv320aic3254-i2s-configuration

器件型号:TLV320AIC3254主题中讨论的其他器件: CC2640R2F、 CC2640、 CC3200AUDBOOST

您好!

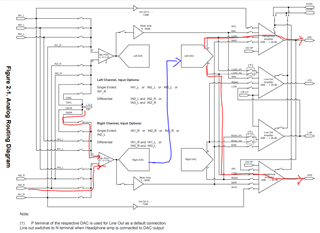

我正在尝试 通过 I2S 在 TLV320AIC3254和 STM32WB55RG 之间进行通信。

问题是 TLV 配置为16kHz 和16位 I2S、与德州仪器 MCU 配合使用时、声音质量会大幅下降。 我已经尝试了 I2S 在两侧的参数(STM32和 TLV)、但我无法找到使其正常工作的方法。

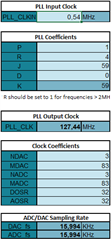

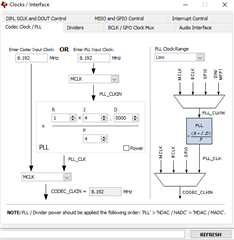

WB55在 I2S 主控模式下配置为16kHz 和16位。 我将 BCLK IN 输入用于 TLV320AIC3254的内部 PLL。

WB55的内部时钟似乎被定义为48MHz、WB55的 BCLK 输出为540kHz、WCLK 输出为16kHz。

我还尝试使用 Excel 来帮助计算 PLL 值、但没有成功。

在 TLV PLL 寄存器的配置方面是否可以获得一些帮助 ?

此致、

Andrew Sonzogoni