https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1187237/tlv320aic3104-pll-configuration

器件型号:TLV320AIC3104尊敬的先生或女士:

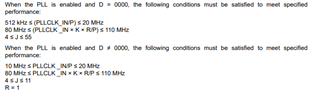

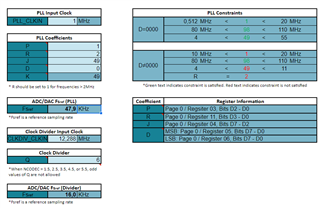

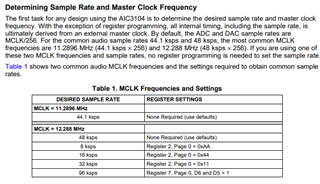

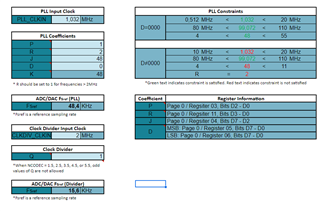

我目前正在使用 TLV320AIC3104、我想使用 PLL 来生成音频时钟。 我提供512kHz MCLK、我希望采样频率为16kHz (数据宽度为16位)。 我不明白我应该如何计算不同的系数。 我尝试了 xlsx 文件、但仍然找不到任何匹配的组合。

您能向我解释一下这一切是如何工作的?

祝你度过美好的一天!

此致、

William。