尊敬的 e2e 支持:

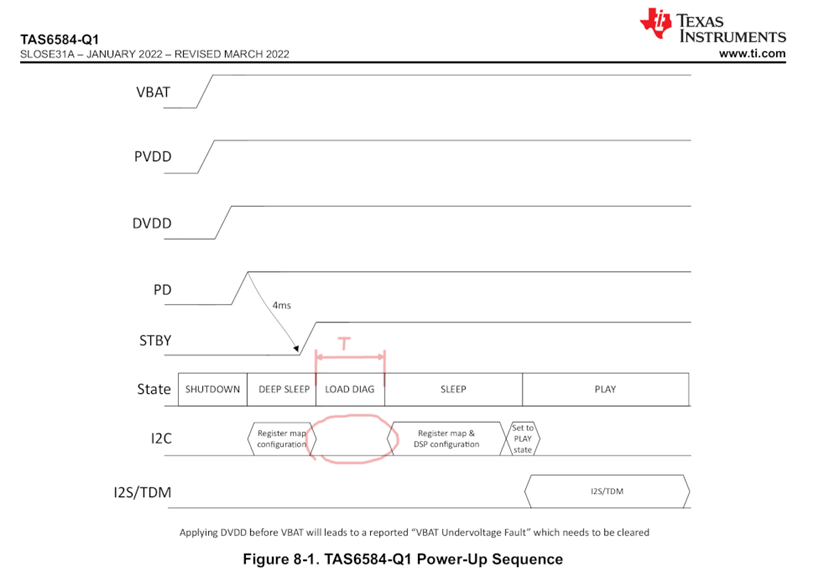

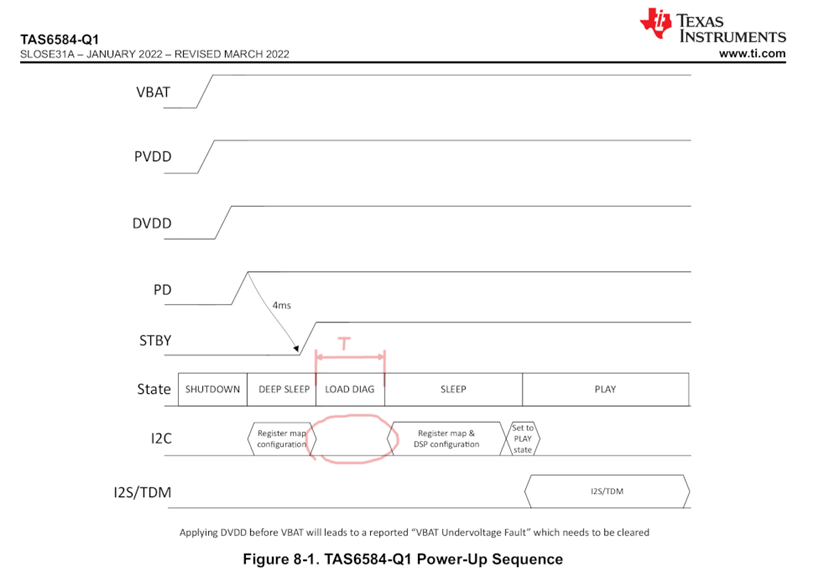

在图8-1中、有该时序图:

在 LOAD DIAG 状态期间、不对 i2c 进行通信。 这引起了一些问题:

- TAS 是否会在该状态下忽略所有通信?

- 如果我询问 TAS 在负载 DIAG 期间的状态变化、它是被锁存还是会在末尾应用、还是被忽略了?

- 假设每个通道都连接了一个扬声器、那么负载 DIAG 状态可以持续多长时间?

此致、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 e2e 支持:

在图8-1中、有该时序图:

在 LOAD DIAG 状态期间、不对 i2c 进行通信。 这引起了一些问题:

此致、

您好!

请查看我的以下评论。

否、器件不能忽略直流诊断期间的任何通信。

您可以通过寄存器0xB0中止直流诊断。

如果负载没有错误、则4通道通常需要155ms 的时间才能完成直流诊断。

您好、Yanming:

感谢您的答复、我还有两个关于此主题的问题

1) 1)我尝试了各种负载配置、以了解进行负载诊断所需的时间:

-所有通道连接后,时间约为150毫秒,正如你所说的

-通道1断开连接时, 无论其他通道是否断开连接,大约需要300毫秒

-在通道2、3和4之间断开一个或多个通道的情况下,大约需要250毫秒

通道之间的这种不对称是否正常?

2) 2)在启动时、我要做的第一件事是上升 PD 引脚并使用 I2C 对 TAS 寄存器进行编程。 在进行一些分析时、我注意到:

https://i.postimg.cc/7LgMJrFH/Microsoft-Teams-image.png

在前5次微控制器尝试写入 TAS 寄存器时、 尽管 PD 已完全启动、但会失败、然后在这些尝试后、连接会正常工作。 这是有原因的吗? 是否应该在 PD 启动后等待一段时间、然后再对 TAS 进行编程?

e2e.ti.com/.../MicrosoftTeams_2D00_image.zip

Derek 你好,试试这家吧

遗憾的是、我不能分享原理图和代码。

我们继续调查该问题、并注意到原理图中 TAS 之间的唯一区别是用于 I2C 地址的电阻。

似乎 TAS 的电阻与0欧姆不同(上拉或下拉)在 PD 升高后需要至少180us 才能开始与 I2C 通信。 而具有0欧姆电阻的 TAS 在小于40us 后即可就绪。

这对您是否有任何意义? I2C 地址电阻值是否可能会影响 TAS 准备好通信之前的时间?

影子的评论是有意义的。 当 PD 拉至高电平时、数字复位仍需要一些时间、然后内部检测和比较器 将锁存 I2C 地址。

经设计团队确认、PD 为高电平并且 I2C 通信正常后、200us 是安全时间。

[/报价]影子表示"他们"建议等待10毫秒。

查看 此处:

Shadow 说:

说到上电序列、我们建议在上拉 PDN 引脚后等待10ms、然后开始其他操作。 不仅是您提到的地址检测、还有其他 LDO 需要一定的时间才能完全准备好。

我不知道"他们"指的是谁。

您说您和设计团队说过、他们确认200us 足够了。 shadow 说10ms 更好。 他是否和您谈到的同一个设计团队进行过交谈?

200ms 足够了吗?或者您是否需要10ms?

您好

我们在大约5ms (i2c @400kHz)下测量寄存器写入、电路板上有4 TAS。

总共约20ms。 将每个 TAS 相加4ms、我们得到36ms。

在任何情况下、我们在寄存器编程后(以及额外的等待后)提高 STBY。 因此可以保证在 PDN 提升和 STBY 提升之间存在超过4ms。

所以问题是:在200us 之后从提高 PDN 到在4ms 之前对寄存器进行编程是否可靠且安全? 有哪些缺点?

换句话说、我们希望尽可能缩短 PDN 提出和 STBY 提出之间的时间(显然不小于4ms)、因此、我们将尽快开始写入寄存器(如您所知、PDN 提出后200us)。 这有多安全可靠?

此致