“线程:C2000WARE”中讨论的其它部件

您好,

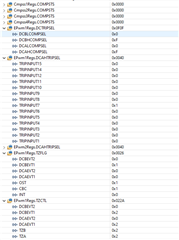

我注意到我在 XbarRegs.XBARFLG1中的所有 CMPSX CTRIPL 标志都是真的,我认为它们应该是假的。

这是我设置 CMPSS 的代码。 我正在反向比较低,我正在尝试使用 CTRIPL 来检查我的值是否低于 DACL。 我这样做对吗? (代码主要来自通用电机控制实验室,对 CMpss 功能没有修改)。

void HAL_setupCMPSSs(HAL_MTR_Handle handle) {

HAL_MTR_Obj *obj = (HAL_MTR_Obj*) handle;

#if defined(MOTOR1_ISBLDC) || defined(MOTOR1_DCLINKSS)

// Refer to the Table 9-2 in Chapter 9 of TMS320F28004x

// Technical Reference Manual (SPRUI33B), to configure the ePWM X-Bar

#if defined(BSXL8323RS_REVA) || defined(BSXL8323RH_REVB)

uint16_t cmpsaDACL = MTR1_CMPSS_DACL_VALUE;

ASysCtl_selectCMPLPMux(MTR1_IDC_CMPLP_SEL, MTR1_IDC_CMPLP_MUX);

// Enable CMPSS and configure the negative input signal to come from the DAC

CMPSS_enableModule(obj->cmpssHandle[0]);

// NEG signal from DAC for COMP-L

CMPSS_configLowComparator(obj->cmpssHandle[0], CMPSS_INSRC_DAC);

// Configure the output signals. Both CTRIPH/L and CTRIPOUTH/L will be fed by

// the asynchronous comparator output.

// Dig filter output ==> CTRIPL, Dig filter output ==> CTRIPOUTL

CMPSS_configOutputsLow(obj->cmpssHandle[0],

CMPSS_TRIP_FILTER |

CMPSS_TRIPOUT_FILTER |

CMPSS_INV_INVERTED);

// Configure digital filter. For this example, the maxiumum values will be

// used for the clock prescale, sample window size, and threshold.

// Initialize the filter logic and start filtering

CMPSS_configFilterLow(obj->cmpssHandle[0], 32, 32, 30);

CMPSS_initFilterLow(obj->cmpssHandle[0]);

// Set up COMPHYSCTL register

// COMP hysteresis set to 2x typical value

CMPSS_setHysteresis(obj->cmpssHandle[0], 1);

// Use VDDA as the reference for the DAC and set DAC value to midpoint for

// arbitrary reference

CMPSS_configDAC(obj->cmpssHandle[0],

CMPSS_DACREF_VDDA | CMPSS_DACVAL_SYSCLK | CMPSS_DACSRC_SHDW);

// Set DAC-L to allowed MAX -ve current

CMPSS_setDACValueLow(obj->cmpssHandle[0], cmpsaDACL);

// Clear any low comparator digital filter output latch

CMPSS_clearFilterLatchLow(obj->cmpssHandle[0]);

#else

#error This board doesn't support single shunt

#endif // BSXL8323RS_REVA || BSXL8323RH_REVB

#else // !(MOTOR1_ISBLDC || MOTOR1_DCLINKSS)

// Refer to the Table 9-2 in Chapter 9 of TMS320F28004x

// Technical Reference Manual (SPRUI33B), to configure the ePWM X-Bar

uint16_t cmpsaDACH = MTR1_CMPSS_DACH_VALUE;

uint16_t cmpsaDACL = MTR1_CMPSS_DACL_VALUE;

uint16_t cnt;

if(handle == hal.mtrHandle[MTR_1]) {

ASysCtl_selectCMPHPMux(MTR1_IU_CMPHP_SEL, MTR1_IU_CMPHP_MUX);

ASysCtl_selectCMPLPMux(MTR1_IU_CMPLP_SEL, MTR1_IU_CMPLP_MUX);

ASysCtl_selectCMPHPMux(MTR1_IV_CMPHP_SEL, MTR1_IV_CMPHP_MUX);

ASysCtl_selectCMPLPMux(MTR1_IV_CMPLP_SEL, MTR1_IV_CMPLP_MUX);

// ASysCtl_selectCMPHPMux(MTR1_IW_CMPHP_SEL, MTR1_IW_CMPHP_MUX);

// ASysCtl_selectCMPLPMux(MTR1_IW_CMPLP_SEL, MTR1_IW_CMPLP_MUX);

} else if(handle == hal.mtrHandle[MTR_2]) {

#ifdef MTR2

cmpsaDACH = MTR2_CMPSS_DACH_VALUE;

cmpsaDACL = MTR2_CMPSS_DACL_VALUE;

ASysCtl_selectCMPHPMux(MTR2_IU_CMPHP_SEL, MTR2_IU_CMPHP_MUX);

ASysCtl_selectCMPLPMux(MTR2_IU_CMPLP_SEL, MTR2_IU_CMPLP_MUX);

ASysCtl_selectCMPHPMux(MTR2_IV_CMPHP_SEL, MTR2_IV_CMPHP_MUX);

ASysCtl_selectCMPLPMux(MTR2_IV_CMPLP_SEL, MTR2_IV_CMPLP_MUX);

// ASysCtl_selectCMPHPMux(MTR2_IW_CMPHP_SEL, MTR2_IW_CMPHP_MUX);

// ASysCtl_selectCMPLPMux(MTR2_IW_CMPLP_SEL, MTR2_IW_CMPLP_MUX);

#endif

}

DEVICE_DELAY_US(500);

for (cnt = 0; cnt < 2; cnt++) {

// Set DAC-H to allowed MAX +ve current

CMPSS_setDACValueHigh(obj->cmpssHandle[cnt], cmpsaDACH);

// Set DAC-L to allowed MAX -ve current

CMPSS_setDACValueLow(obj->cmpssHandle[cnt], cmpsaDACL);

// NEG signal from DAC for COMP-H

CMPSS_configHighComparator(obj->cmpssHandle[cnt], CMPSS_INSRC_DAC);

// NEG signal from DAC for COMP-L

CMPSS_configLowComparator(obj->cmpssHandle[cnt], CMPSS_INSRC_DAC | CMPSS_INV_INVERTED); //CMPSS_INV_INVERTED

// Enable CMPSS and configure the negative input signal to come from the DAC

CMPSS_enableModule(obj->cmpssHandle[cnt]);

// Configure digital filter. For this example, the maxiumum values will be

// used for the clock prescale, sample window size, and threshold.

CMPSS_configFilterHigh(obj->cmpssHandle[cnt], 32, 32, 30);

CMPSS_initFilterHigh(obj->cmpssHandle[cnt]);

// Initialize the filter logic and start filtering

CMPSS_configFilterLow(obj->cmpssHandle[cnt], 32, 32, 30);

CMPSS_initFilterLow(obj->cmpssHandle[cnt]);

// Configure the output signals. Both CTRIPH and CTRIPOUTH will be fed by

// the asynchronous comparator output.

// Dig filter output ==> CTRIPH, Dig filter output ==> CTRIPOUTH

CMPSS_configOutputsHigh(obj->cmpssHandle[cnt], CMPSS_TRIP_FILTER); // | CMPSS_TRIPOUT_FILTER

// Dig filter output ==> CTRIPL, Dig filter output ==> CTRIPOUTL

CMPSS_configOutputsLow(obj->cmpssHandle[cnt], CMPSS_TRIP_FILTER);

// Set up COMPHYSCTL register

CMPSS_setHysteresis(obj->cmpssHandle[cnt], 2);

// Use VDDA as the reference for the DAC and set DAC value to midpoint for

// arbitrary reference

CMPSS_configDAC(obj->cmpssHandle[cnt], CMPSS_DACREF_VDDA | CMPSS_DACVAL_SYSCLK | CMPSS_DACSRC_SHDW);

// Clear any high comparator digital filter output latch

CMPSS_clearFilterLatchHigh(obj->cmpssHandle[cnt]);

// Clear any low comparator digital filter output latch

CMPSS_clearFilterLatchLow(obj->cmpssHandle[cnt]);

}

#endif // !(MOTOR1_ISBLDC || MOTOR1_DCLINKSS)

return;

} // end of HAL_setupCMPSSs() function

我认为 ADC 值应该与其当前的 DACH 和 DACL 值进行比较:

用于配置 ADC 和 CMpss 的值:

#define MTR1_IU_ADCRESLT MTR1_IU_ADCRES_BASE + ADC_O_RESULT1 // ADCA-A11*/C0-SOC1 #define MTR1_IV_ADCRESLT MTR1_IV_ADCRES_BASE + ADC_O_RESULT1 // ADCC-A14/C4* -SOC1 #define MTR2_IU_ADCRESLT MTR2_IU_ADCRES_BASE + ADC_O_RESULT5 // ADCA-A10/C10*-SOC2 #define MTR2_IV_ADCRESLT MTR2_IV_ADCRES_BASE + ADC_O_RESULT5 // ADCC-A9*/C8 -SOC3 // CMPSS #define MTR1_IU_CMPHP_SEL ASYSCTL_CMPHPMUX_SELECT_1 // CMPSS1-A11 #define MTR1_IU_CMPLP_SEL ASYSCTL_CMPLPMUX_SELECT_1 // CMPSS1-A11, N/A #define MTR1_IV_CMPHP_SEL ASYSCTL_CMPHPMUX_SELECT_3 // CMPSS3-C4 #define MTR1_IV_CMPLP_SEL ASYSCTL_CMPLPMUX_SELECT_3 // CMPSS3-C4 #define MTR1_IU_CMPHP_MUX 1 // CMPSS1-A11 #define MTR1_IU_CMPLP_MUX 1 // CMPSS1-A11 #define MTR1_IV_CMPHP_MUX 4 // CMPSS3-C4 #define MTR1_IV_CMPLP_MUX 4 // CMPSS3-C4 #define MTR1_CMPSS_DACH_VALUE 2048+1024+512 #define MTR1_CMPSS_DACL_VALUE 2048-1024-512 #define MTR2_IU_CMPHP_SEL ASYSCTL_CMPHPMUX_SELECT_2 // CMPSS2-C10 #define MTR2_IU_CMPLP_SEL ASYSCTL_CMPLPMUX_SELECT_2 // CMPSS2-C10, N/A #define MTR2_IV_CMPHP_SEL ASYSCTL_CMPHPMUX_SELECT_4 // CMPSS4-A9 #define MTR2_IV_CMPLP_SEL ASYSCTL_CMPLPMUX_SELECT_4 // CMPSS4-A9 #define MTR2_IU_CMPHP_MUX 3 // CMPSS2-C10 #define MTR2_IU_CMPLP_MUX 3 // CMPSS2-C10 #define MTR2_IV_CMPHP_MUX 0 // CMPSS4-A9 #define MTR2_IV_CMPLP_MUX 0 // CMPSS4-A9 #define MTR2_CMPSS_DACH_VALUE 2048+1024+512 #define MTR2_CMPSS_DACL_VALUE 2048-1024-512

谢谢,