“线程:C2000WARE”中讨论的其它部件

您好,专家,

我向大家提出了我的问题,我已经使用 DAC 的阈值配置了多个比较器。 我想知道哪个比较器触发了我的问题。 请帮帮我。

我还有三个其他信号通过 TZ1|,TZ2|和 TZ3|连接到 Tripzone。

我想在触发 TZ 和/或 CMSS 信号时关闭 ePWM。 关闭操作正确。 因此,我按如下方式配置了 CMPSSS (请参见代码中的 cmps_init 和 cmps_actions 函数)。 我在不同的 TRIPIN 信号和 ePWM_TZ_SIGNAL_DCBEVT1事件上链接了每个 CMPSSS。 通过查看数字比较子模块的文档,我认为我可以在 XbarRegs.XBARFLG1.bit 寄存器中读取此触发器信息。

这是正确的吗?

初始化时,比较器寄存器的位数为1是否正常?

如果我只使用函数 XBAR_clearInputFlag (XBAR_INPUM_FLG_CMSSx)将它们设置为0。 它似乎在我的代码中起作用(在某些情况下,我有一个在初始化时保持较高的输出)。

我也无法解释这一点吗?

另一方面,当我触发 CMPSS1时,我无法在无限循环中重置它,为什么?

寄存器 XbarRegs.XBARFLG1.bit 中的位仍为1。 我使用函数 XBAR_getInputFlagStatus(x)来知道触发了哪个比较器。

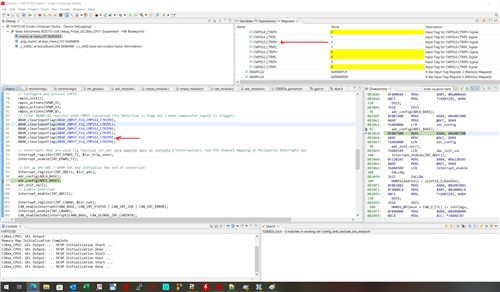

在初始化时,我想通过 XBAR_ClearInputFlag 重置 CMPSSS 输出,但我遇到一个问题,即在重置功能后,一个或两个输出处于较高水平(请参阅屏幕截图)。

感谢你的帮助

达米恩

void cmpss_init()

{

// Enable CMPSS and configure the negative input signal to come from the DAC

CMPSS_enableModule(CMPSS1_BASE);

CMPSS_enableModule(CMPSS2_BASE);

CMPSS_enableModule(CMPSS3_BASE);

CMPSS_enableModule(CMPSS4_BASE);

// Use VDDA as the reference for the DAC and set DAC value to midpoint for arbitrary reference.

CMPSS_configDAC(CMPSS1_BASE, CMPSS_DACREF_VDDA);

CMPSS_configDAC(CMPSS2_BASE, CMPSS_DACREF_VDDA);

CMPSS_configDAC(CMPSS3_BASE, CMPSS_DACREF_VDDA);

CMPSS_configDAC(CMPSS4_BASE, CMPSS_DACREF_VDDA);

// To use CMP1_HP2 pin A6 for MU_TRAC_BATT_PCH

ASysCtl_selectCMPHPMux(ASYSCTL_CMPHPMUX_SELECT_1, 2);

// To use CMP1_LP3 pin A15/C7 for MU_FUEL_CELL_PCH

ASysCtl_selectCMPLPMux(ASYSCTL_CMPLPMUX_SELECT_1, 3);

// To use CMP3_HP1 pin A5/C2 for MI_L_W

ASysCtl_selectCMPHPMux(ASYSCTL_CMPHPMUX_SELECT_3, 1);

// To use CMP2_HP1 pin A12/C1 for MI_L_U

ASysCtl_selectCMPHPMux(ASYSCTL_CMPHPMUX_SELECT_2, 1);

// To use CMP2_LP4 pin A8/C11 for MI_L_V

ASysCtl_selectCMPLPMux(ASYSCTL_CMPLPMUX_SELECT_2, 4);

// To use CMP4_HP1 pin A7/C3 for MI_TRAC_BATT

ASysCtl_selectCMPHPMux(ASYSCTL_CMPHPMUX_SELECT_4, 1);

// Configure the output signals. Both CTRIPH will be fed by the asynchronous comparator output.

//1

THRESHOLD_MU_TRAC_BATT_PCH_DIGITAL = (THRESHOLD_MU_TRAC_BATT_PCH * 8.2 * 0.000332 * ADC_RESOLUTION) / FULL_SCALE;

CMPSS_configHighComparator(CMPSS1_BASE, CMPSS_INSRC_DAC); // Threshold drive by GPIO or input DAC

CMPSS_setDACValueHigh(CMPSS1_BASE, THRESHOLD_MU_TRAC_BATT_PCH_DIGITAL); // Define threshold associated

CMPSS_configOutputsHigh(CMPSS1_BASE, CMPSS_TRIP_SYNC_COMP); // Set output comparator (synchronous or asynchronous)

//2

THRESHOLD_MU_FUEL_CELL_PCH_DIGITAL = (THRESHOLD_MU_FUEL_CELL_PCH * 8.2 * 0.000332 * ADC_RESOLUTION) / FULL_SCALE;

CMPSS_configLowComparator(CMPSS1_BASE, CMPSS_INSRC_DAC); // Threshold drive by GPIO or input DAC

CMPSS_setDACValueLow(CMPSS1_BASE, THRESHOLD_MU_FUEL_CELL_PCH_DIGITAL); // Define threshold associated

CMPSS_configOutputsLow(CMPSS1_BASE, CMPSS_TRIP_SYNC_COMP); // Set output comparator (synchronous or asynchronous)

// Configure the output signals. Both CTRIPH will be fed by the asynchronous comparator output.

//1

THRESHOLD_MI_L_U_DIGITAL = (((THRESHOLD_MI_L_U * 0.625 / 200) + REF_MI_H_2V5) * ADC_RESOLUTION) / FULL_SCALE;

CMPSS_configHighComparator(CMPSS2_BASE, CMPSS_INSRC_DAC); // Threshold drive by GPIO or input DAC

CMPSS_setDACValueHigh(CMPSS2_BASE, THRESHOLD_MI_L_U_DIGITAL); // Define threshold associated

CMPSS_configOutputsHigh(CMPSS2_BASE, CMPSS_TRIP_SYNC_COMP); // Set output comparator (synchronous or asynchronous)

//2

THRESHOLD_MI_L_V_DIGITAL = (((THRESHOLD_MI_L_V * 0.625 / 200) + REF_MI_H_2V5) * ADC_RESOLUTION) / FULL_SCALE;

CMPSS_configLowComparator(CMPSS2_BASE, CMPSS_INSRC_DAC); // Threshold drive by GPIO or input DAC

CMPSS_setDACValueLow(CMPSS2_BASE, THRESHOLD_MI_L_V_DIGITAL); // Define threshold associated

CMPSS_configOutputsLow(CMPSS2_BASE, CMPSS_TRIP_SYNC_COMP); // Set output comparator (synchronous or asynchronous)

// Configure the output signals. Both CTRIPH will be fed by the asynchronous comparator output.

//1

THRESHOLD_MI_L_W_DIGITAL = (((THRESHOLD_MI_L_W * 0.625 / 200) + REF_MI_H_2V5) * ADC_RESOLUTION) / FULL_SCALE;

CMPSS_configHighComparator(CMPSS3_BASE, CMPSS_INSRC_DAC); // Threshold drive by GPIO or input DAC

CMPSS_setDACValueHigh(CMPSS3_BASE, THRESHOLD_MI_L_W_DIGITAL); // Define threshold associated

CMPSS_configOutputsHigh(CMPSS3_BASE, CMPSS_TRIP_SYNC_COMP); // Set output comparator (synchronous or asynchronous)

// Configure the output signals. Both CTRIPH will be fed by the asynchronous comparator output.

//1

THRESHOLD_MI_TRAC_BATT_DIGITAL = ((((THRESHOLD_MI_TRAC_BATT * 2 * 301) / 100000) + REF_MI_BT_1V5) * ADC_RESOLUTION) / FULL_SCALE;

CMPSS_configHighComparator(CMPSS4_BASE, CMPSS_INSRC_DAC); // Threshold drive by GPIO or input DAC

CMPSS_setDACValueHigh(CMPSS4_BASE, THRESHOLD_MI_TRAC_BATT_DIGITAL); // Define threshold associated

CMPSS_configOutputsHigh(CMPSS4_BASE, CMPSS_TRIP_SYNC_COMP); // Set output comparator (synchronous or asynchronous)

// Configure TRIP4 to be CTRIP1H using the ePWM X-BAR. Attach CMPSS output to TRIPINx via EPWMXBAR module

XBAR_setEPWMMuxConfig(XBAR_TRIP4, XBAR_EPWM_MUX00_CMPSS1_CTRIPH);

XBAR_setEPWMMuxConfig(XBAR_TRIP5, XBAR_EPWM_MUX01_CMPSS1_CTRIPL);

XBAR_setEPWMMuxConfig(XBAR_TRIP7, XBAR_EPWM_MUX04_CMPSS3_CTRIPH);

XBAR_setEPWMMuxConfig(XBAR_TRIP8, XBAR_EPWM_MUX02_CMPSS2_CTRIPH);

XBAR_setEPWMMuxConfig(XBAR_TRIP9, XBAR_EPWM_MUX03_CMPSS2_CTRIPL);

XBAR_setEPWMMuxConfig(XBAR_TRIP10, XBAR_EPWM_MUX06_CMPSS4_CTRIPH);

// See the ePWM X-BAR Mux configuration table, see Crossbar(X-BAR) doc for more informations

XBAR_enableEPWMMux(XBAR_TRIP4, XBAR_MUX00);

XBAR_enableEPWMMux(XBAR_TRIP5, XBAR_MUX01);

XBAR_enableEPWMMux(XBAR_TRIP7, XBAR_MUX04);

XBAR_enableEPWMMux(XBAR_TRIP8, XBAR_MUX02);

XBAR_enableEPWMMux(XBAR_TRIP9, XBAR_MUX03);

XBAR_enableEPWMMux(XBAR_TRIP10, XBAR_MUX06);

}

void cmpss_actions(uint32_t base)

{

// Configure ePWMx to output low on TZx TRIP

EPWM_setTripZoneAction(base, EPWM_TZ_ACTION_EVENT_TZA, EPWM_TZ_ACTION_LOW);

EPWM_setTripZoneAction(base, EPWM_TZ_ACTION_EVENT_TZB, EPWM_TZ_ACTION_LOW);

// Trigger event when DCBH is high

EPWM_setTripZoneDigitalCompareEventCondition(base, EPWM_TZ_DC_OUTPUT_B1, EPWM_TZ_EVENT_DCXH_HIGH);

// Configure DCBH to use TRIP4 as an input

EPWM_enableDigitalCompareTripCombinationInput(base, EPWM_DC_COMBINATIONAL_TRIPIN4, EPWM_DC_TYPE_DCBH);

EPWM_enableDigitalCompareTripCombinationInput(base, EPWM_DC_COMBINATIONAL_TRIPIN5, EPWM_DC_TYPE_DCBH);

EPWM_enableDigitalCompareTripCombinationInput(base, EPWM_DC_COMBINATIONAL_TRIPIN7, EPWM_DC_TYPE_DCBH);

EPWM_enableDigitalCompareTripCombinationInput(base, EPWM_DC_COMBINATIONAL_TRIPIN8, EPWM_DC_TYPE_DCBH);

EPWM_enableDigitalCompareTripCombinationInput(base, EPWM_DC_COMBINATIONAL_TRIPIN9, EPWM_DC_TYPE_DCBH);

EPWM_enableDigitalCompareTripCombinationInput(base, EPWM_DC_COMBINATIONAL_TRIPIN10, EPWM_DC_TYPE_DCBH);

// Enable DCB as OST

EPWM_enableTripZoneSignals(base, EPWM_TZ_SIGNAL_DCBEVT1);

// Clear trip flags

EPWM_clearTripZoneFlag(base, EPWM_TZ_FLAG_DCBEVT1);

}

#include "cmpss_module.h"

#include "device.h"

#include "adc_module.h"

#include "epwm_module.h"

#include "tripzone_module.h"

#include "can_module.h"

#include "monitoring.h"

#include "sm_global.h"

#include "contactor.h"

#include "timer.h"

void main(void)

{

// Initialize device clock and peripherals

Device_init();

// Disable pin locks and enable internal pullups.

Device_initGPIO();

// Initialize PIE and clear PIE registers. Disables CPU interrupts.

Interrupt_initModule();

// Initialize the PIE vector table with pointers to the shell Interrupt Service Routines (ISR).

Interrupt_initVectorTable();

trip_zone_config();

gpio_precharge_init();

gpio_coldplate_init();

can_init();

// Initialization timer for ISR TX_CAN

timer_cpu_init(CPUTIMER0_BASE);

// Initialization timer for STEP_START_TIMER precharge

timer_cpu_init(CPUTIMER1_BASE);

// Initialization timer for monitoring parameters

timer_cpu_init(CPUTIMER2_BASE);

// Timer for CAN communication Interrupt all of (us) 10ms

timer_cpu_config(CPUTIMER0_BASE, DEVICE_SYSCLK_FREQ, 10000);

// Timer for STEP_START_TIMER precharge all of (us) PARAM_T_PL_US

config_cpu_timer(CPUTIMER1_BASE);

// Timer for CAN all of (us) 10ms

config_cpu_timer(CPUTIMER2_BASE);

Interrupt_register(INT_TIMER0, &isr_timer);

CPUTimer_enableInterrupt(CPUTIMER0_BASE);

Interrupt_enable(INT_TIMER0);

// Start timer for interrupt CAN (to send frames)

CPUTimer_startTimer(CPUTIMER0_BASE);

// Start timer for precharge step (to measure precharge voltage when timer is reached)

CPUTimer_startTimer(CPUTIMER1_BASE);

// Start timer for monitoring

CPUTimer_startTimer(CPUTIMER2_BASE);

// Disable sync and clock to PWM

SysCtl_disablePeripheral(SYSCTL_PERIPH_CLK_TBCLKSYNC);

EALLOW;

//EPWM1

GPIO_setPinConfig(GPIO_0_EPWM1_A);

GPIO_setPinConfig(GPIO_1_EPWM1_B);

//EPWM2

GPIO_setPinConfig(GPIO_41_EPWM2_A);

GPIO_setPinConfig(GPIO_40_EPWM2_B);

//EPWM4

GPIO_setPinConfig(GPIO_22_EPWM4_A);

GPIO_setPinConfig(GPIO_7_EPWM4_B);

EDIS;

epwm_init(SPWM_U, 0);

epwm_init(SPWM_V, EPWM_PHI);

epwm_init(SPWM_W, EPWM_PHI << 1);

// Configure and actions CMPSS

cmpss_init();

cmpss_actions(SPWM_U);

cmpss_actions(SPWM_V);

cmpss_actions(SPWM_W);

// Clear XBARFLG1 register with CMPSS concerned (for detection => flag set 1 when comparator inputs is trigger)

XBAR_clearInputFlag(XBAR_INPUT_FLG_CMPSS1_CTRIPH);

XBAR_clearInputFlag(XBAR_INPUT_FLG_CMPSS1_CTRIPL);

XBAR_clearInputFlag(XBAR_INPUT_FLG_CMPSS2_CTRIPH);

XBAR_clearInputFlag(XBAR_INPUT_FLG_CMPSS2_CTRIPL);

XBAR_clearInputFlag(XBAR_INPUT_FLG_CMPSS3_CTRIPH);

XBAR_clearInputFlag(XBAR_INPUT_FLG_CMPSS4_CTRIPH);

// Interrupts that are used (la fonction isr_adc sera appelée dans un contexte d'interruption). See PIE Channel Mapping in Peripheral Interrupts doc

Interrupt_register(INT_EPWM1_TZ, &isr_trip_zone);

Interrupt_enable(INT_EPWM1_TZ);

// Set up the ADC / ePWM SOC and initialize the end of conversion

Interrupt_register(INT_ADCC1, &isr_adc);

adc_config(ADCA_BASE);

adc_config(ADCC_BASE);

adc_init_soc();

// Enable interrupt

Interrupt_enable(INT_ADCC1);

Interrupt_register(INT_CANA0, &isr_can);

CAN_enableInterrupt(CANA_BASE, CAN_INT_STATUS | CAN_INT_IE0 | CAN_INT_ERROR);

Interrupt_enable(INT_CANA0);

CAN_enableGlobalInterrupt(CANA_BASE, CAN_GLOBAL_INT_CANINT0);

// Enable sync and clock to PWM

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_TBCLKSYNC);

// Start CAN module operations

CAN_startModule(CANA_BASE);

// Enable Global Interrupt (INTM) and realtime interrupt (DBGM)

EINT;

ERTM;

GPIO_setPinConfig(GPIO_14_GPIO14); // toggle pin for debug

GPIO_setDirectionMode(14, GPIO_DIR_MODE_OUT);

GPIO_setPadConfig(14, GPIO_PIN_TYPE_STD);

GPIO_writePin(14, 0);

GPIO_setPinConfig(GPIO_15_GPIO15); // toggle pin for debug

GPIO_setDirectionMode(15, GPIO_DIR_MODE_OUT);

GPIO_setPadConfig(15, GPIO_PIN_TYPE_STD);

GPIO_writePin(15, 0);

GPIO_setPinConfig(GPIO_16_GPIO16); // toggle pin for debug

GPIO_setDirectionMode(16, GPIO_DIR_MODE_OUT);

GPIO_setPadConfig(16, GPIO_PIN_TYPE_STD);

GPIO_writePin(16, 0);

GPIO_setPinConfig(GPIO_6_GPIO6); // toggle pin for debug

GPIO_setDirectionMode(6, GPIO_DIR_MODE_OUT);

GPIO_setPadConfig(6, GPIO_PIN_TYPE_STD);

GPIO_writePin(6, 0);

while(1)

{

monitoring_hysteresis(&mu_trac_batt_ovp, XBAR_INPUT_FLG_CMPSS1_CTRIPH, &MU_TRAC_BATT_PCH_FLT, &mu_trac_batt_state);

//monitoring_hysteresis(&mu_fuel_cell_ovp, XBAR_INPUT_FLG_CMPSS1_CTRIPL, &MU_FUEL_CELL_PCH_FLT, &mu_fuel_cell_state);

//monitoring_hysteresis(&mi_l_u_ocp, XBAR_INPUT_FLG_CMPSS2_CTRIPH, &MI_L_U_FLT, &mi_l_u_state);

//monitoring_hysteresis(&mi_l_v_ocp, XBAR_INPUT_FLG_CMPSS2_CTRIPL, &MI_L_V_FLT, &mi_l_v_state);

//monitoring_hysteresis(&mi_l_w_ocp, XBAR_INPUT_FLG_CMPSS3_CTRIPH, &MI_L_W_FLT, &mi_l_w_state);

// Slow monitoring

detection_coldplate(cold_plate_pin, &cold_plate_detect, &cold_plate_state_error);

// First parameter is a structure input and the second is a global pointer to transmit to isr_timer (CAN)

detection_contactor(&k_line_batt, &k_line_batt_state_error);

detection_contactor(&k_line_fuel_cell, &k_line_fc_state_error);

detection_contactor(&k_pl_batt, &k_pl_batt_state_error);

detection_contactor(&k_pl_fuel_cell, &k_pl_fc_state_error);

sm_main();

// Wait while eWPM4 causes conversion and if trip zone is set shoot down ePWM

// Trip flag is set when CTRIP signal is asserted

if((EPWM_getTripZoneFlagStatus(SPWM_U) & EPWM_TZ_FLAG_DCBEVT1) != 0U || (EPWM_getTripZoneFlagStatus(SPWM_V) & EPWM_TZ_FLAG_DCBEVT1) != 0U || (EPWM_getTripZoneFlagStatus(SPWM_W) & EPWM_TZ_FLAG_DCBEVT1) != 0U)

{

// Clear trip flags

EPWM_clearTripZoneFlag(SPWM_U, EPWM_TZ_FLAG_DCBEVT1 | EPWM_TZ_FLAG_OST);

EPWM_clearTripZoneFlag(SPWM_V, EPWM_TZ_FLAG_DCBEVT1 | EPWM_TZ_FLAG_OST);

EPWM_clearTripZoneFlag(SPWM_W, EPWM_TZ_FLAG_DCBEVT1 | EPWM_TZ_FLAG_OST);

}

}

}