请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TMS320F280025C 您好!

我有一个引导加载程序、当我不使用 DCSM 时、该引导加载程序相当不错(直接包含在项目中、如下 所示:https://www.ti.com/lit/an/spracp8a/spracp8a.pdf?ts=1656879106556)

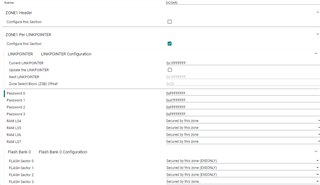

我的 DCSM 设置如下所示:

引导加载程序链接器脚本如下所示:

-stack 0x380

MEMORY

{

BEGIN : origin = 0x080000, length = 0x000002

BOOT_RSVD : origin = 0x00000002, length = 0x00000126

RAMM0 : origin = 0x00000128, length = 0x000002D8

RAMM1 : origin = 0x00000400, length = 0x000003F8 /* on-chip RAM block M1 */

// RAMM1_RSVD : origin = 0x000007F8, length = 0x00000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

/* RAMLS4 : origin = 0x0000A000, length = 0x00000800

RAMLS5 : origin = 0x0000A800, length = 0x00000800

RAMLS6 : origin = 0x0000B000, length = 0x00000800

RAMLS7 : origin = 0x0000B800, length = 0x00000800*/

/* Combining all the LS RAMs */

RAMLS4567 : origin = 0x0000A000, length = 0x00002000

RAMGS0 : origin = 0x0000C000, length = 0x000007F8

// RAMGS0_RSVD : origin = 0x0000C7F8, length = 0x00000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

BOOTROM : origin = 0x003F0000, length = 0x00008000

BOOTROM_EXT : origin = 0x003F8000, length = 0x00007FC0

RESET : origin = 0x003FFFC0, length = 0x00000002

/* Flash sectors */

/* BANK 0 */

FLASH_BANK0_SEC0 : origin = 0x080002, length = 0x000FFE /* on-chip Flash */

FLASH_BANK0_SEC1 : origin = 0x081000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC2 : origin = 0x082000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC3 : origin = 0x083000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC4 : origin = 0x084000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC5 : origin = 0x085000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC6 : origin = 0x086000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC7 : origin = 0x087000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC8 : origin = 0x088000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC9 : origin = 0x089000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC10 : origin = 0x08A000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC11 : origin = 0x08B000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC12 : origin = 0x08C000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC13 : origin = 0x08D000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC14 : origin = 0x08E000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC15 : origin = 0x08F000, length = 0x000FF0 /* on-chip Flash */

// FLASH_BANK0_SEC15_RSVD : origin = 0x08FFF0, length = 0x000010 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

}

SECTIONS

{

.reset : > RESET, TYPE = DSECT /* not used, */

codestart : > BEGIN, ALIGN(4)

.TI.ramfunc : LOAD = (FLASH_BANK0_SEC0 | FLASH_BANK0_SEC1 | FLASH_BANK0_SEC2), /* This sector is loaded from flash to RAM */

RUN = RAMLS4567,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(8)

.text : >> FLASH_BANK0_SEC0 | FLASH_BANK0_SEC1 | FLASH_BANK0_SEC2, ALIGN(8) /* Programm is in flash */

.cinit : > FLASH_BANK0_SEC2, ALIGN(4)

.switch : > FLASH_BANK0_SEC2, ALIGN(4)

.cio : > FLASH_BANK0_SEC2

.pinit : > FLASH_BANK0_SEC2 ALIGN(4)

.const : > FLASH_BANK0_SEC2, ALIGN(4)

.init_array : > FLASH_BANK0_SEC2, ALIGN(4)

.stack : > RAMM1

.bss : > RAMM0

.bss:output : > RAMM0

.bss:cio : > RAMM0

.data : > RAMM0 /* Seems not to work, when using AES data --> leads to CRC error while updating, why? --> Needs separate RAM */

.sysmem : > RAMM0

ramgs0 : > RAMGS0

/* Allocate IQ math areas: */

IQmath : > RAMM0

IQmathTables : > RAMM0

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/

codestart.asm:

;//########################################################################### ;// ;// FILE: flash_kernel_ex3_codestartbranch.asm ;// ;// TITLE: Branch for redirecting code execution after boot. ;// ;// For these examples, code_start is the first code that is executed after ;// exiting the boot ROM code. ;// ;// The codestart section in the linker cmd file is used to physically place ;// this code at the correct memory location. This section should be placed ;// at the location the BOOT ROM will re-direct the code to. For example, ;// for boot to FLASH this code will be located at 0x80000. ;// ;// In addition, the example f28002x projects are setup such that the codegen ;// entry point is also set to the codestart label. This is done by linker ;// option -e in the project build options. When the debugger loads the code, ;// it will automatically set the PC to the "entry point" address indicated by ;// the -e linker option. In this case the debugger is simply assigning the PC, ;// it is not the same as a full reset of the device. ;// ;// The compiler may warn that the entry point for the project is other then ;// _c_init00. _c_init00 is the C environment setup and is run before ;// main() is entered. The codestart code will re-direct the execution ;// to _c_init00 and thus there is no worry and this warning can be ignored. ;// ;//########################################################################### ;// $Copyright: ;// Copyright (C) 2021 Texas Instruments Incorporated - http://www.ti.com/ ;// ;// Redistribution and use in source and binary forms, with or without ;// modification, are permitted provided that the following conditions ;// are met: ;// ;// Redistributions of source code must retain the above copyright ;// notice, this list of conditions and the following disclaimer. ;// ;// Redistributions in binary form must reproduce the above copyright ;// notice, this list of conditions and the following disclaimer in the ;// documentation and/or other materials provided with the ;// distribution. ;// ;// Neither the name of Texas Instruments Incorporated nor the names of ;// its contributors may be used to endorse or promote products derived ;// from this software without specific prior written permission. ;// ;// THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS ;// "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT ;// LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR ;// A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT ;// OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, ;// SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT ;// LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, ;// DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY ;// THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT ;// (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE ;// OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE. ;// $ ;//########################################################################### *********************************************************************** WD_DISABLE .set 1 ;set to 1 to disable WD, else set to 0 .ref _c_int00 .ref main .global load_app_jump_addr .global code_start .global ExitBoot *********************************************************************** * Function: codestart section * * Description: Branch to code starting point *********************************************************************** .sect "codestart" .retain code_start: .if WD_DISABLE == 1 LB wd_disable ;Branch to watchdog disable code .else LB _c_int00 ;Branch to start of boot._asm in RTS library ;LCR main .endif ;end codestart section *********************************************************************** * Function: wd_disable * * Description: Disables the watchdog timer *********************************************************************** .if WD_DISABLE == 1 .text load_app_jump_addr: LB ExitBoot wd_disable: SETC OBJMODE ;Set OBJMODE for 28x object code EALLOW ;Enable EALLOW protected register access MOVZ DP, #7029h>>6 ;Set data page for WDCR register MOV @7029h, #0068h ;Set WDDIS bit in WDCR to disable WD EDIS ;Disable EALLOW protected register access LB _c_int00 ;Branch to start of boot._asm in RTS library ;LCR main ; Cleanup and exit. At this point the EntryAddr ; is located in the ACC register ;BF ExitBoot, UNC .endif ;end wd_disable ;loadApplication: ; Cleanup and exit. At this point the EntryAddr ; is located in the ACC register ;BF ExitBoot, UNC ;----------------------------------------------- ; ExitBoot ;----------------------------------------------- ;----------------------------------------------- ;This module cleans up after the boot loader ; ; 1) Make sure the stack is deallocated. ; SP = 0x400 after exiting the boot ; loader ; 2) Push 0 onto the stack so RPC will be ; 0 after using LRETR to jump to the ; entry point ; 2) Load RPC with the entry point ; 3) Clear all XARn registers ; 4) Clear ACC, P and XT registers ; 5) LRETR - this will also clear the RPC ; register since 0 was on the stack ;----------------------------------------------- ExitBoot: __stack: .usect ".stack",0 ;----------------------------------------------- ; Insure that the stack is deallocated ;----------------------------------------------- MOV SP,#__stack ;----------------------------------------------- ; Clear the bottom of the stack. This will endup ; in RPC when we are finished ;----------------------------------------------- MOV *SP++,#0 MOV *SP++,#0 ;----------------------------------------------- ; Load RPC with the entry point as determined ; by the boot mode. This address will be returned ; in the ACC register. ;----------------------------------------------- PUSH ACC POP RPC ;----------------------------------------------- ; Put registers back in their reset state. ; ; Clear all the XARn, ACC, XT, and P and DP ; registers ; ; NOTE: Leave the device in C28x operating mode ; (OBJMODE = 1, AMODE = 0) ;----------------------------------------------- ZAPA MOVL XT,ACC MOVZ AR0,AL MOVZ AR1,AL MOVZ AR2,AL MOVZ AR3,AL MOVZ AR4,AL MOVZ AR5,AL MOVZ AR6,AL MOVZ AR7,AL MOVW DP, #0 ;------------------------------------------------ ; Restore ST0 and ST1. Note OBJMODE is ; the only bit not restored to its reset state. ; OBJMODE is left set for C28x object operating ; mode. ; ; ST0 = 0x0000 ST1 = 0x0A0B ; 15:10 OVC = 0 15:13 ARP = 0 ; 9: 7 PM = 0 12 XF = 0 ; 6 V = 0 11 M0M1MAP = 1 ; 5 N = 0 10 reserved ; 4 Z = 0 9 OBJMODE = 1 ; 3 C = 0 8 AMODE = 0 ; 2 TC = 0 7 IDLESTAT = 0 ; 1 OVM = 0 6 EALLOW = 0 ; 0 SXM = 0 5 LOOP = 0 ; 4 SPA = 0 ; 3 VMAP = 1 ; 2 PAGE0 = 0 ; 1 DBGM = 1 ; 0 INTM = 1 ;----------------------------------------------- MOV *SP++,#0 MOV *SP++,#0x0A0B POP ST1 POP ST0 ;------------------------------------------------ ; Jump to the EntryAddr as defined by the ; boot mode selected and continue execution ;----------------------------------------------- LRETR ;eof ---------- .end ;// ;// End of file. ;//

那么、复位怎么会不再工作呢? DCSM 是否以某种方式移动了所有地址、并且无法跳转至开始?