主题中讨论的其他器件: ADC34J25

尊敬的产品线工程师

我的客户对 LMK04828有以下问题。

"您能帮我仔细检查该器件能否为正常时钟生成10MHz 频率? 我的意思是,我不想使用 JESD SYSREF/SYNC 函数。”

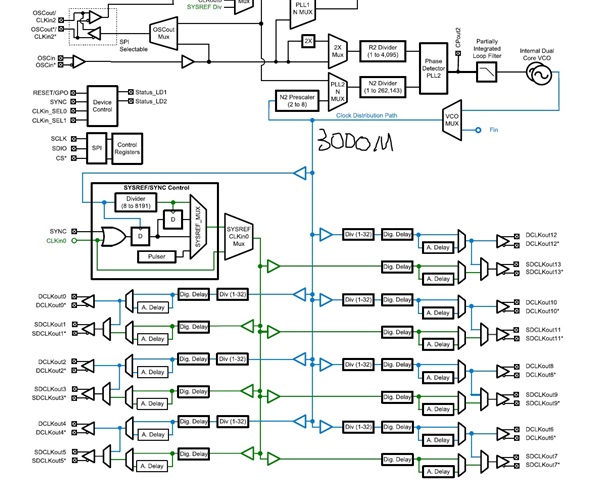

此处所需的 VCO 频率为3000MHz。

非常感谢!

此致、

Bill

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你(们)好、Noel

我是来自飞利浦的射频工程师 Brooke。 我在条例草案中提出这项质询。 感谢您的讲解。

此处的 VCO1输出指定为3000MHz、因此我使用 SDCLK 分频器获取用于 ADC/DAC 的300m 和150m 时钟。

从您的回答中、我能否确认此10MHz 时钟可用于器件时钟? 我想使用此10MHz 来驱动 PCB 板上的其他器件。

如何将芯片的 SYSREF/SYNC 部分设置为使用10MHz 作为器件时钟? 在硬件中将10MHz 用于器件时钟时、应注意哪些事项?

此10MHz 频率是否会获得高于300m 和150m 的采样相位噪声/抖动性能?

感谢您的回复。

此致、

Brooke

您好、Brooke、

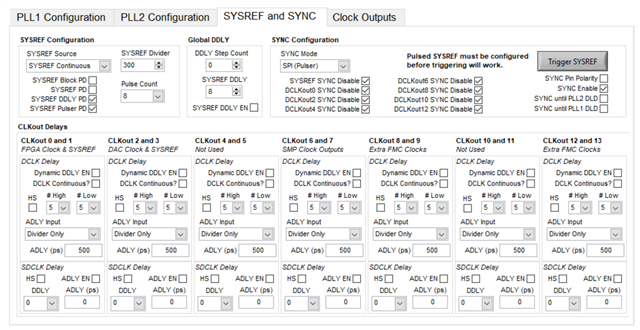

SYSREF 模块可配置为生成连续时钟或脉冲。 如上图所示、我们只需使用 SYSREF 模块的分频器对 VCO 时钟进行分频。 SDCLKout1的输出是一个连续10MHz 时钟。

SYSREF 分频器具有与时钟分频器相同的性能、其附加抖动几乎相同。

建议使用 TICS Pro 设置所需的配置、以便获得正确的寄存器设置。 很难通过读取数据表来设置正确的寄存器设置。

你(们)好、Noel

感谢您的快速信赖。

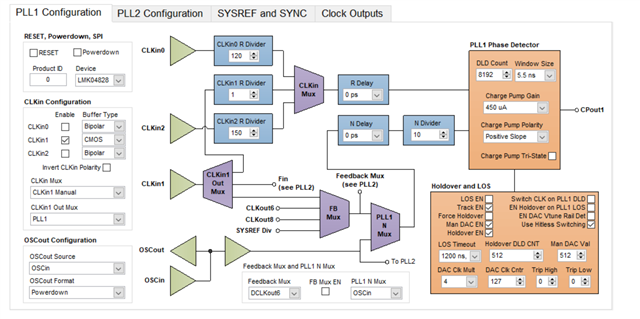

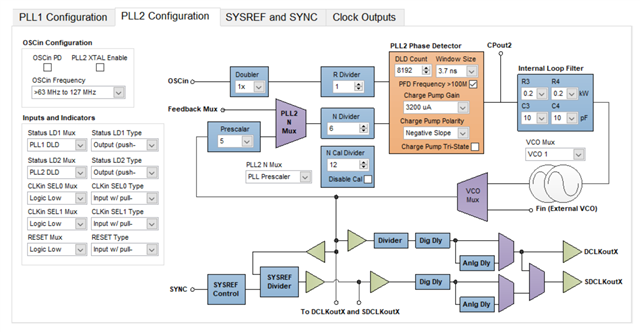

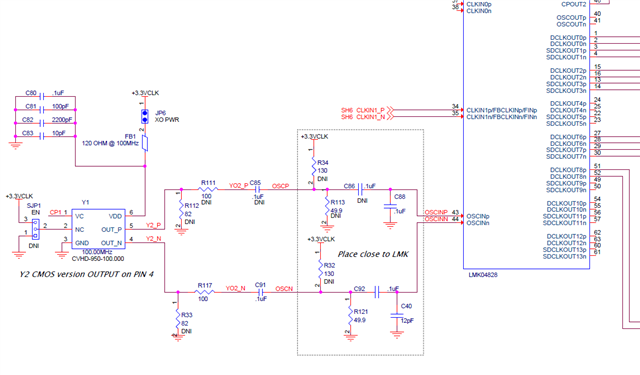

我手上有一个 ADC34J25演示板、它具有 LMK04828。 在这里、我想使用外部参考时钟(来自 Keysight N9010A 10MHz 输出)来锁定 PLL1和 PLL2。 在这里、我想为 LMK04828使用双环路模式。 此演示板具有一个用于 PLL1的100MHz VCXO。

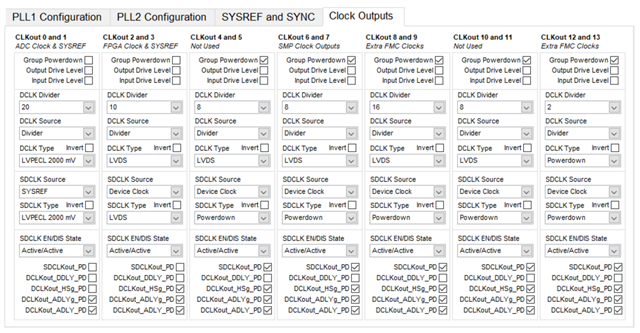

请参阅以下 PLL1、PLL2、SYSREF/SYNC 和 CLK 输出的配置:

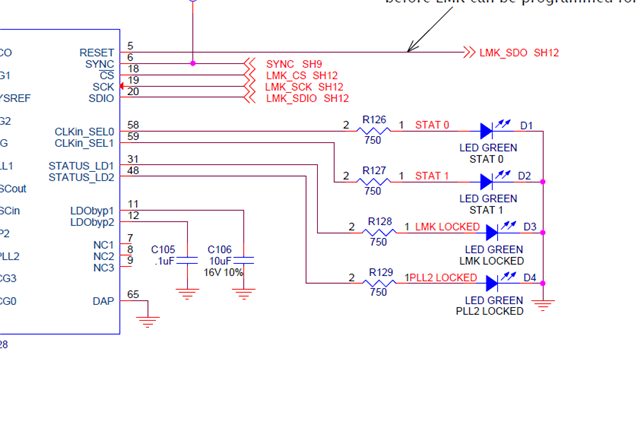

在演示板中、我可以看到 LED D4为绿色、而 LED D1、D2和 D3未打开。

从我的角度来看、我认为 LMK04828现在还没有锁定。

请帮我检查 LMK04828的上述配置吗? 感谢你能抽出时间。

请参阅下面有关 PLL1的 VCXO 部件

您好、Brooke、

能否共享用于 LMK04828编程的配置文件以查看寄存器写入详细信息?

从配置映像中、对于 PLL1锁定、STATUS_LD1 (D3)应打开、并且似乎未锁定 PLL1。

下面是快速更新的配置文件 FYR。您可以转换为 ADC GUI 预期的配置格式、并更改适当的输出通道、然后在您的板中尝试。

e2e.ti.com/.../LMK04828_5F00_10MCLKin1_5F00_100MOSCin_5F00_10MSYSREF.tcse2e.ti.com/.../LMK04828_5F00_10MCLKin1_5F00_100MOSCin_5F00_10MSYSREF.txt

谢谢!

此致、

Ajeet Pal

您好、Brooke、

为 PLL1的数字锁定检测设置 PLL1_WND_SIZE。 根据 PLL1基准和反馈之间的相位误差设置的窗口大小。 如果它们之间存在更多相位误差、则需要增大窗口大小。STATUS_LD1将显示 PLL1的锁定检测。 PLL1_WND_SIZE POR 默认值为0x3、并保持不变、窗口大小越小、PFD 频率越高。

是的、如果 STATUS_LD1 (D3)处于打开状态、则表示针对给定设置锁定了 PLL1。

谢谢!

此致、

Ajeet Pal