主题中讨论的其他器件: LMK5C33216、 LMK5B33216、 LMK05028、 LMK5B12204、 LMK04033、 LMK04000、 LMK04001、 LMK04011、 LMK04010、 LMK04002、 LMK04031、 LMK04610、 CDCE813-Q1

您好的团队:

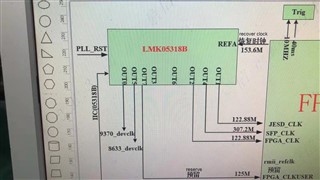

我想确认是否有一个小于1W 的低功耗器件 来替代 LMK05318B。

TKS、供您确认。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好的团队:

我想确认是否有一个小于1W 的低功耗器件 来替代 LMK05318B。

TKS、供您确认。

您好、Allen、

您能否提供有关所需频率计划的更多信息?

您的 XO 输入频率是多少?

需要多少个输出、有多少频率?

3.所需的输出格式(LVDS、LVPECL、HCSL 等)是什么?

4.您是否需要 DPLL? 如果是、您的参考频率是多少?

根据您的配置、LMK05318B 的功耗可能低于1W。

您还能提供输出时钟所需的输出抖动性能吗?

我们的大多数网络同步器器件都需要3.3V 电源、因此功耗可能大于1W、但如果性能不是很重要、则有一些选项支持更低的电源电压、因此功耗更低。

另请注意、以下链接显示了我们所有供您参考的时钟抖动清除器和同步器: 时钟抖动清除器和同步器

此致、

起亚拉赫巴

您好、Allen、

下面的演示介绍了如何使用 LMK05318B GUI:

e2e.ti.com/.../LMK05318B-TICS-Pro-GUI-Overview.pdf

以下链接显示了我们的所有时钟抖动清除器和同步器: TI 时钟抖动清除器和同步器

所有器件的功耗都可能大于1W。

要获得低于1W 的功率、您需要使用更少的输出、单个 PLL 和低电流图输出格式(例如 LVDS)。

例如 、数据表中的第11.2节提供了用于计算 LMK05318B 的近似功耗的公式。

使用上述公式并将器件配置为仅使用 APLL1、仅使用 OUT0/OUT1和 LVDS 输出格式、功率如下。

我们有:

如您所见、即使使用2个输出和单个 PLL、此器件仍将高于1W 的功耗。

我们的所有其他网络同步器(LMK5B12204、LMK05028、LMK5B33216、LMK5C33216)也会发生同样的情况。

因此、如果您需要具有 DPLL 的器件(网络同步器)、您很可能具有高于1W 的功耗。

我们的抖动清除器(LMK04000、LMK04001、LMK04002、LMK04010、LMK04011、 LMK04031、LMK04033)的功耗也将高于1W。

这些抖动清除器的电流消耗如下所示:

如果我们取最小的335mA 值、我们仍然得到等于1.1055W (335mA * 3.3V)的功耗。

我们的抖动清除器和网络同步器器件很少具有低于1W 功耗的原因是它们具有3.3V 电源。

LMK04610 将是您的最佳且唯一的选择(具有3路输出的 CDCE813-Q1除外)。

LMK04610的功耗如下所示:

此致、

起亚拉赫巴

您好、Allen、

要禁用 APLL1并仅使用 APLL2、必须执行以下操作:

1.在 APLL1页上禁用 APLL1,如下所示。

2.启用 APLL2并将 PLL2参考选择设置 为"XO"。 如果 PLL2参考选择 设置为"VCO1-级联模式(默认)"、则不会从 APLL2获取输出时钟、因为其参考为 APLL1且 APLL1已禁用。

出于以下原因、我强烈建议不要这样做:

1.如果只使用 APLL2、则将无法使用 DPLL。

2.如果只使用 APLL2,则输出时钟相位噪声性能将比使用 APLL1差。

使用 APLL2而不是 APLL1和 DPLL 时、电流消耗实际上更大。 正如您在下图中看到的、APLL2在启用时使用120mA 的电流。 启用时、APLL1和 DPLL 使用110mA 的电流。 禁用时、APLL2使用20mA 电流。 禁用后、APLL1和 DPLL 仍将消耗20mA 电流(数据表中未指定此值、但我已在我们的实验中进行了验证)。

我建议仅使用 APLL2的唯一情况是、如果您的所有输出频率都不是 APLL1 2.5GHz BAW VCO 的整数除法。 在这种情况下、在数学上无法使用 APLL1、因此您只需默认为 APLL2。

如果您的频率是2.5 GHz BAW VCO 的整数除法、那么我强烈建议仅使用 APLL1。

此致、

起亚拉赫巴

您好起亚:

许多细节说明。 我想与您再次确认 将 BAW 频率锁定检测设置作为附加文件。

客户反馈、如果他们禁用此设置、则 Opto 模块的终端设备将变得更加不稳定。

但是、如果启用此设置、则光耦模块将变得更加稳定。

但是、基于 SW,中的此说明、DPLL (客户需要启用)与 BAW 频率锁定检测性能之间存在冲突。

在本例中、您是否会帮助检查此计时配置文件和 B/D? 太棒了!