您好!

我有一个抖动的10kHz 参考时钟、我想使用它来生成/约束数十 kHz 范围内的多个同步时钟(例如、40kHz、40kHz、有点相位、80kHz、120kHz)。

我已经评估了 LMK05318、但遗憾的是、它在千赫兹范围内只有一个可用输出。 您会推荐什么器件?

谢谢、

Steve

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我有一个抖动的10kHz 参考时钟、我想使用它来生成/约束数十 kHz 范围内的多个同步时钟(例如、40kHz、40kHz、有点相位、80kHz、120kHz)。

我已经评估了 LMK05318、但遗憾的是、它在千赫兹范围内只有一个可用输出。 您会推荐什么器件?

谢谢、

Steve

您好、Steve、

您请求的频率范围没有太多选项。

此致、

Derek Payne

尊敬的 Derek:感谢您的全面回答。

我的输出抖动要求相当宽松:< 1ns、但也不会受到预算的过度限制(易用性和上市时间更重要)。

我应以 几十或几百千赫(40、80 120只是任意数字)的速率独立为 DAC 和 ADC (如果使用该类型的 ADC、则加上 Δ-Σ 时钟)计时、但这些速率必须与恢复的参考10kHz 输入同步。

我可以使用 PGA280或其他零漂移器件等器件、我相信、同步计时也会带来好处。

当无法推导基准信号时、我还需要一个10kHz 输出作为 CPU 中断。 总之(例如):

输入

10 kHz

输出

10kHz (CPU 中断)

80kHz (LDAC)

120kHz (CONV)

1MHz (PGA280时钟)

48MHz (Δ-Σ)

LMK04208是否 能够做到这一点?

谢谢、此致、

Steve

您好、Steve、

鉴于新的频率范围也包括10kHz、因此获取所需的每个频率变得非常困难。 我认为 LMK04208无法满足您的需求。 下面提供了说明和其他指导。

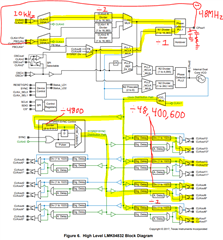

根据初始指导、LMK04832或 LMK04208似乎可用于生成所需的频率。 数据表中的参数可能会尝试在使用集成 VCO 的双环路模式下提供最小输出频率;即使是这样、我也希望 LMK04832根据 VCO 范围更接近0.24kHz ... 无论如何、这并不是输出结构的实际限制。 LMK04832或 LMK04208上的输出、尤其是 在 LVCMOS 模式下、可以根据需要降低频率。

但是、现在的限制是、48MHz 和10kHz 来自同一器件、这意味着需要至少4800分频。 在 LMK04208上没有创建4800分频的机制、这将允许在同一器件上生成48MHz 和10kHz 频率。

LMK04832具有一个13位 SYSREF 分频器(8192)、因此如果 VCXO 频率更改为48MHz、该方案仍适用于 LMK04832。 SYSREF 分频器可以像常规分频器一样以连续模式运行、并且还具有一个缓冲器、将 SYSREF 频率复制到反馈多路复用器、以用作 PLL1反馈。 其余的10位分频器(1024)足以生成1MHz、120kHz 和80kHz、并针对48MHz 使用额外的1分频。

我还附加了 TICS Pro 配置、以展示如何在 LMK04832中实现这一操作。

e2e.ti.com/.../LMK04832-config.tcs

LMK04832解决方案可能会随着时间的推移而出现一些额外的频率计划变化、但对于某些较低频率的分频、例如40kHz、可能需要在输出端添加一个或多个 D 触发器以略微扩展分频比。 此外、编程序列会有一个简短的附录、以确保分频器全部同步。 如果 CPU 中断时钟需要持续运行、 同步序列的时序可能会受到影响; 在实践中、我不希望同步序列正确会带来一定的挑战、尤其是在启动时允许初始化时钟的情况下、任何内容都取决于它们的输出。

另一个注意事项:48MHz 不是 VCXO 值的常见值、因此分销商不太可能携带它立即订购。 您可能需要与 VCXO 供应商联系以获取样片以进行快速测试。 我想有一些来自 SiTime 的可编程 VCXO、它们可以立即订购并单独编程。 无论如何、 VCXO 的采购策略可能是该解决方案最困难的方面。

LMK5C33216仍然能够 实现您的频率计划、但同样、该器件的功能非常超出您的需求、如果时钟无法以不同的格式提供、则需要对 LVCMOS 进行一些转换。 然而、LMK5C33216基本上可以生成您需要的任何低频时钟、而不管它们是如何变化的。 在 TICS Pro 中测试输出配置工具时、我发现使该工具为我提供所需的配置有点困难。 我最终得到了一个有效的配置、但 该工具似乎存在一些错误、使器件配置变得不必要的挑战。 如果您确实想测试此器 件、只需做好准备;该工具处于这样的状态、一旦频率规划已知、您可能需要 TI 的一些帮助来生成配置。 我已注意到该工具的问题、我们正在进行修复、但部署更新版本可能需要几周时间。 您仍然应该能够对配置(包括任何 TI 生成的配置)进行编程、而只是在受影响的工具中自行创建配置。

使用 LMK05318和 LMK01801时、LMK05318可生成48MHz 和10kHz;PLL1可生成25MHz 输出、该输出可在 LMK01801的一半上分频为1MHz;LMK01801的另一半可将4.8MHz 分频为120kHz 和80kHz。 除了48MHz 之外、所有这些信号都可以是 LVCMOS、但48MHz 可能可以接受为不同的格式。 以上所述、根据您对 频率潜在变化的评论、随着频率规划的发展、如果分压器分压比停止有利、则很难使该解决方案发挥作用。 如果需要在该解决方案的输出端添加触发器、我认为它会失去很多好处; 唯一的剩余优势是使用 DPLL 锁定基准、但除非您需要保持或 DCO 等更复杂的功能、否则我不确定这确实是一个优势。

基于 LMK05318的配置最复杂的方面是控制所有输出时钟的精确相位对齐。 它们将被锁频、但是鉴于它们在不同器件间的分布以及 LMK05318或 LMK01801的3/4组上缺少数字延迟、确保它们是锁相可能是一个挑战。

总之:从易用 性和快速开发的角度来看、假设您可以获得48MHz VCXO、我怀疑在上述配置中使用 LMK04832可能会更简单。 实际上、在 LMK5C33216EVM 上进行测试的速度可能最快、因为不需要更改器件;但是、我不会将其称为最简单的选项。

希望这可以清除问题、并为您做出决策提供一些基础。

此致、

Derek Payne