请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMX2594 主题中讨论的其他器件: LMX2820

大家好!

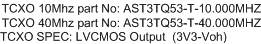

我在设计中使用以下时钟方案。

由于 LMX2594接受 CLKIN 电压(2VPP)在 TCXO 输出端提供衰减器、以匹配 LMX2594 CLK 输入的电压电平

在时钟输出端保持50欧姆的布线长度阻抗后、衰减器是否会影响相位噪声?

下面是时钟方案和 TCXO 器件型号。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.