请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:AMC7836 您好,

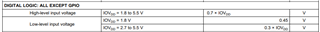

我正在将 AMC7836与 FPGA 连接,在计算噪声边界时发现,AMC7836数字输入的高侧噪声边界小于100mV,这将是我们设计中的一个问题。 所以我想知道数字 IOS 指定的 V_IH 和 V_IL 的吸收电流是多少? 如果实际汇电流高,电压要求可能会降低。 我的理解是否正确?

谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,萨马加拉,

我不确定我是否准确理解您的问题。

我们的数字逻辑引脚(不包括 GPIO)的泄漏电流最大为±5 µA,因此您不会期望逻辑高时的吸入电流超过5 µA,逻辑低时的吸入电流不少于5 µA。 48kΩ~kΩ 器具有48 μ A 的集成拉电流,因此您不会期望任何数字输出需要为逻辑高电流提供大量电流,并且它必须在逻辑低电流时吸收 I = IOVDD/μ A 电流。

这能回答你的问题吗?

谢谢,

保罗