请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DAC38J84 大家好、

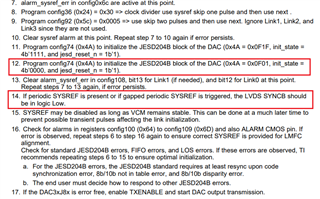

我将根据 SLAA696 DAC38J84器件初始化和 sysref 配置评估 DAC38J84。 但是、我遇到了几个问题。 您能帮我解决这些问题吗?

1、SYNCB 将在第12步后被拉低。 这将导致通信重新连接。 FPGA 将持续发送重新连接请求。

2、您能不能帮助我解释第14步、我不理解这一步。

谢谢和 BR。

达信

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Marsh

[引用 userid="496209" URL"~/support/data-trlers-group/data-reachers/f/data-reachers-forum/1107100/dac38j84-dac38j84-device-initializing-and-sysref-configure-consides">1、在第12步之后、SYNCB 将被拉低。 这将导致通信重新连接。 FPGA 将持续发送重新连接请求。正确。 当 SYNCB 处于逻辑低电平时、FPGA 应根据 JESD204B 标准发送 K28.5字符

步骤14基本上说 SYSREF 将初始化 JESD204B 状态机、并触发 SYNCB 为逻辑低电平以触发同步重新连接请求。