主题中讨论的其他器件: ADS54J60、 TI-JESD204-IP

您好!

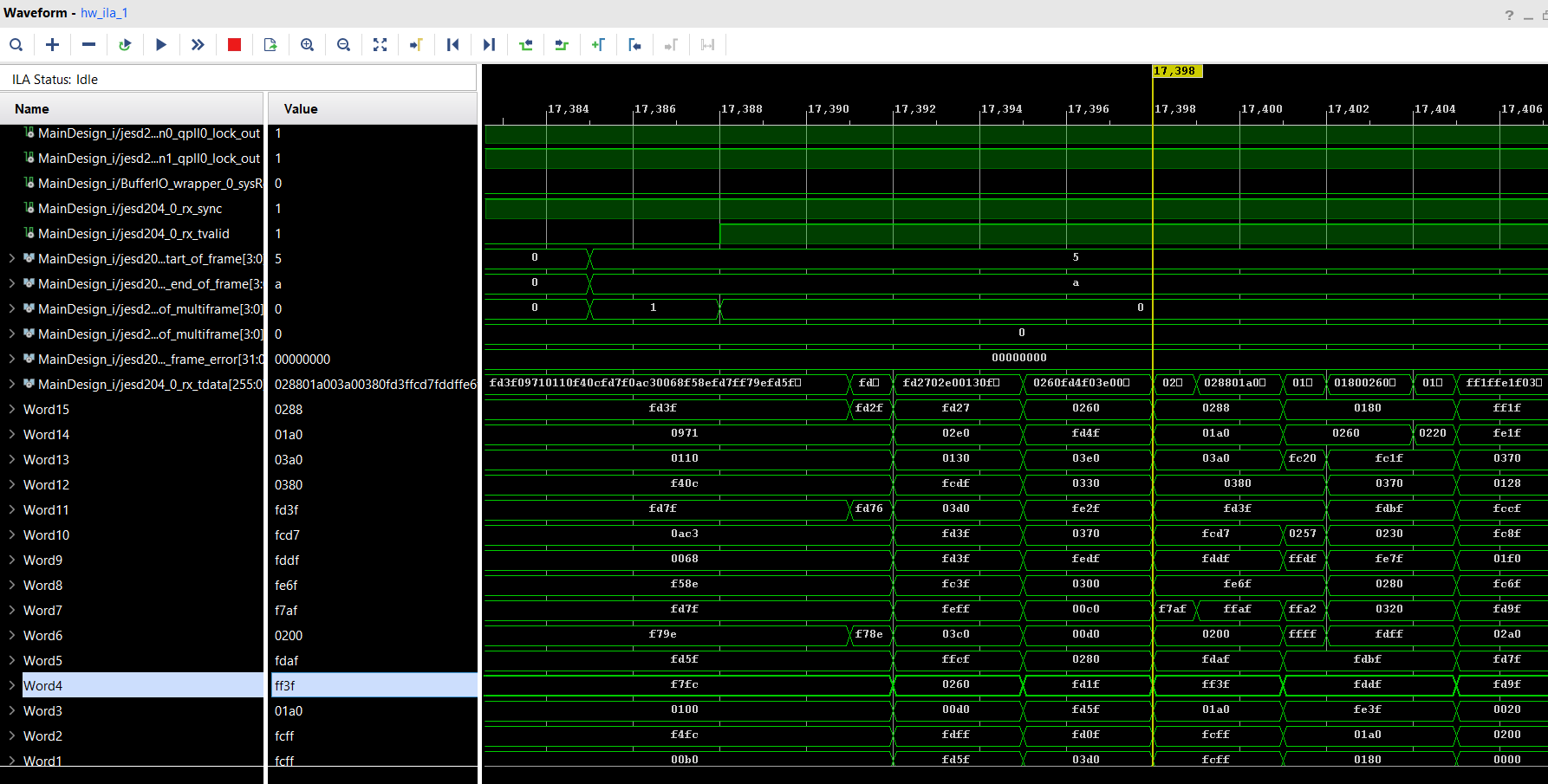

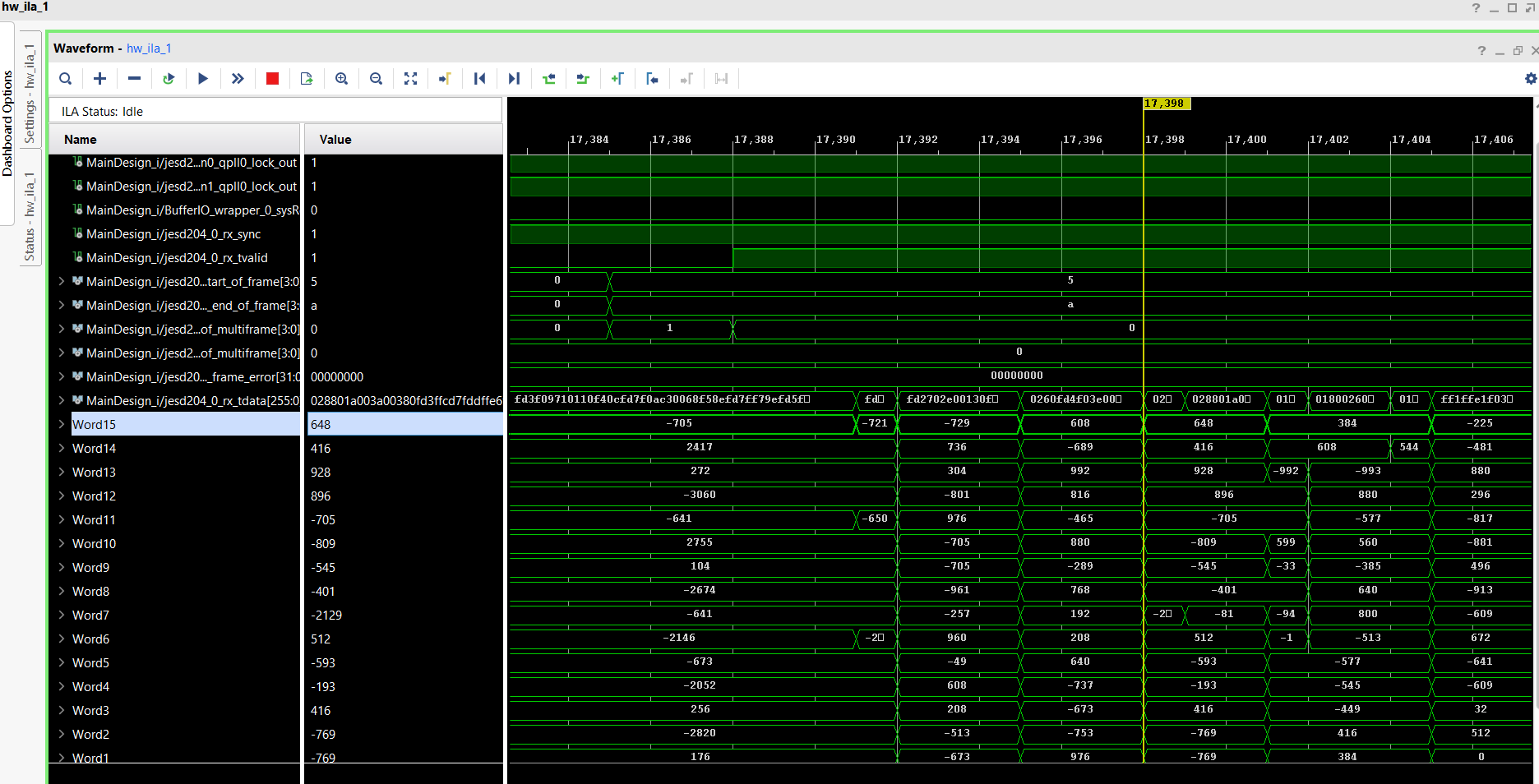

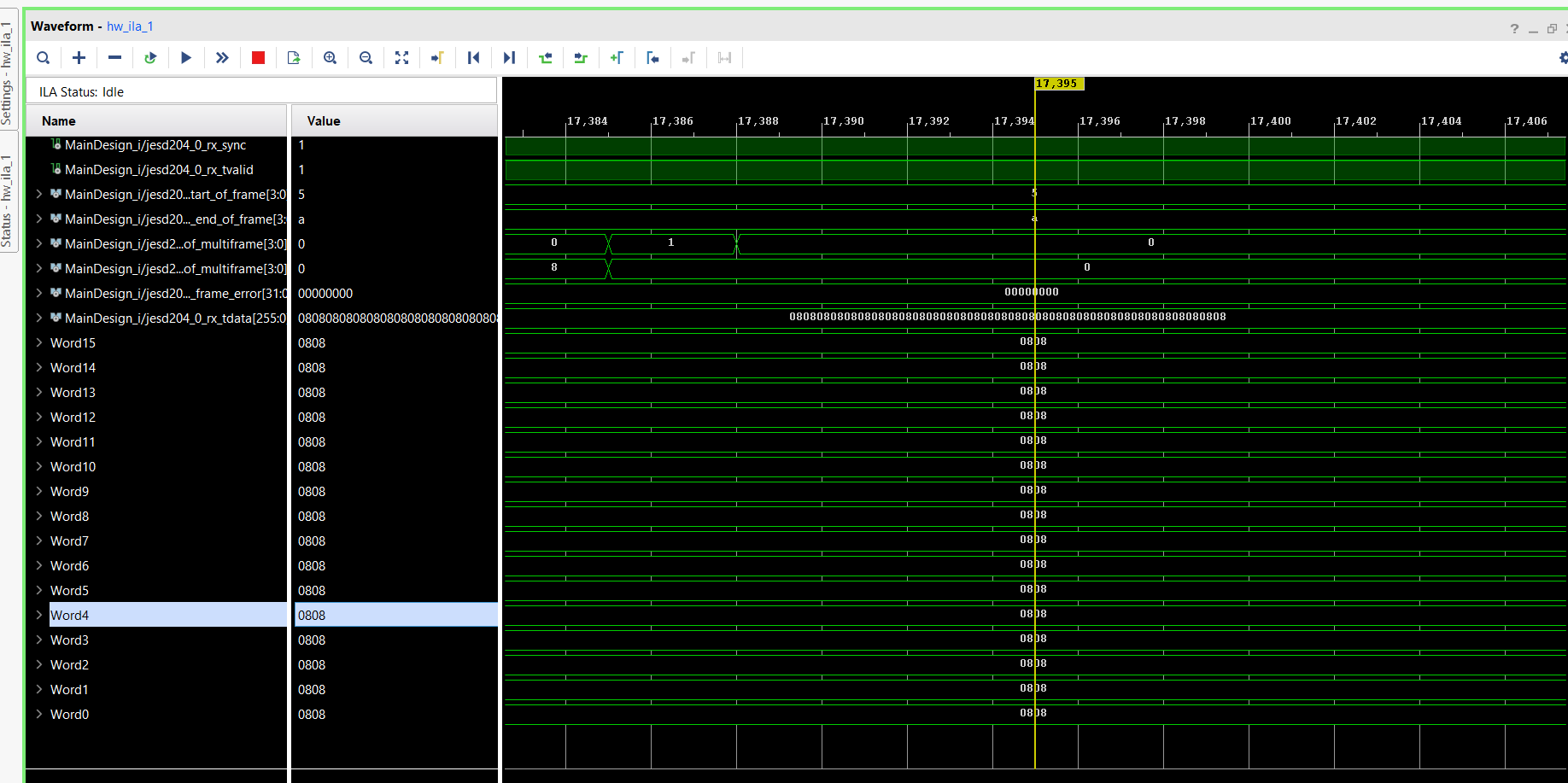

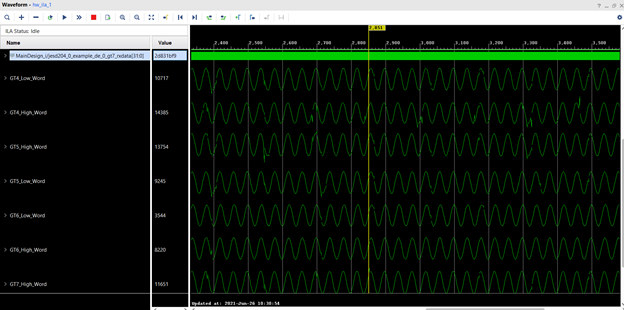

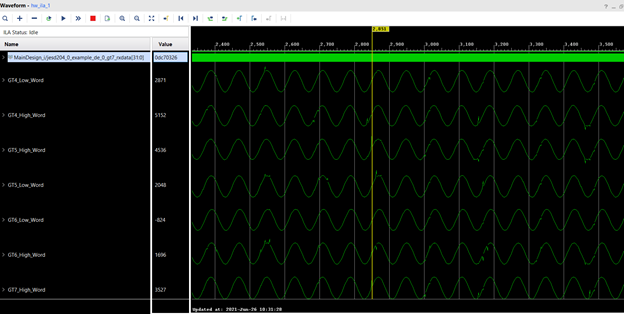

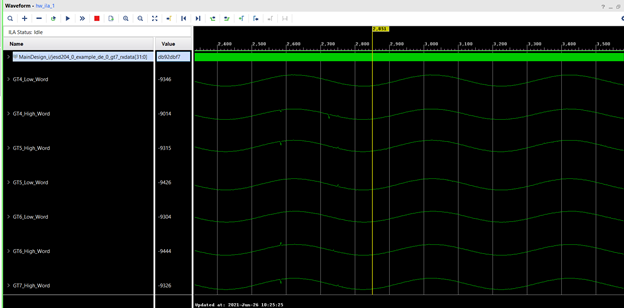

我将 TSW54J60EVM 和 Avnet FPGA 开发板用于高速 ADC 数据 采集系统。 我使用 TI 的 ADC54JXXEVM 软件设置 ADC/PLL 参数。 在 FPGA 端、使用了 JESD Rx 内核。 测试条件为:JP2短路(ADC1具有零输入)。 JP1开路、一个10MHz、20mVpp 正弦信号被发送到 J3/INBP。 无到 J4/INBM 的输入信号。 我正在使用 FPGA ILA 来捕获 ADC 数据。 我从 JESD rxCore 获得了 rxData。 但我不确定如何确认这些数据。 我的问题是:

1) ADC 数据的格式是什么:它是2的补充 吗?

2) 2)什么是 ADC 数据帧序列? 即 ADC 数据顺序? rxData 的每个存储器中都有256位。 它可以看到上128位和下128位用于两个 ADC 通道。 但我不知道128位内的序列(8个16位 ADC 数据)

3) 3) 当我单击 ADC 设置页面上的“翻转 ADC 数据”选项时,我确实观察到 ADC 数据发生翻转;MSB 变为 LSB。 这是否意味着 TI 演示板和 Xilinx FPGA 板之间的 JESD204正常工作? 在 FPGA JESD Rx 内核中、Rx_SYNC 和 Rx_tVALID 始终为高电平。

随附的是 FPGA 上的 ILA 图像、TSW54J60EVM 上的 JESD204设置以及 Vivado IP 上的 JESD204设置。

如果有人提出建议、请就此向我提供帮助。 我已经在这上面停留了一段时间。

非常感谢您的参与。

-Y 型