您好!

我希望有人能帮助我解决我们最近发现的这个问题。

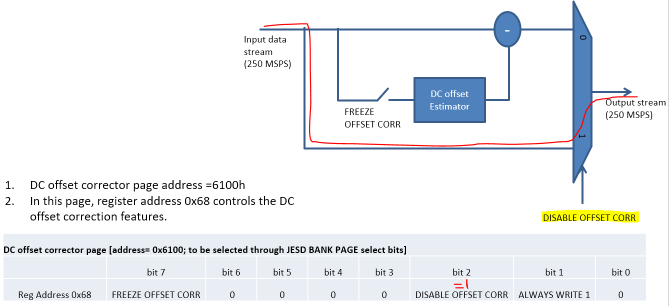

我们将在直流耦合设计中使用 ADS54J40。 我们仅使用通道 A、我们可以禁用的通道 B 的所有功能都将被禁用。 我们已禁用 VCM 补偿(主页寄存器0x4F = 0x01)并 完全绕过交错偏移校正(寄存器0x6068 = 0x06)

在我们的大多数模块中、这种方法都非常有效(~75%、尚无大量统计数据)。 稳定的直流输入可提供稳定的原始 ADC 输出、噪声仅为几 LSB。

但是、在某些模块中、我们会看到奇怪的偏移跳跃。 这是一个非常常规的模式、至少2个不同模块都是相同的模式:每1.6秒有40ms 的时间周期、ADC 输出将跳转。

甚至令人感到奇怪的是、这似乎仅在 ADC 差分输入电压处于~+0.53V 至+0.89V 范围内时发生。 在该电压范围之外,我们不会观察到跳变。

下表显示了 ADC 上干净 DC +0.756V 差分输入的4个子 ADC 通道输出。

Sub-ADC #2未显示任何跳转,#1和#3显示+61LSB 跳转,而#4显示+100LSB 跳转:

|

正常 |

跳转 |

差动 |

||

|

ADC 原始 LSB |

子 ADC1 |

6602 |

6665 |

62. |

|

子 ADC2 |

6525. |

6525. |

1 |

|

|

子 ADC3 |

6446. |

6508. |

61. |

|

|

子 ADC4 |

6524. |

6624 |

101. |

|

|

平均 |

6524. |

6580 |

56. |

我们已经排除了许多可能导致这种跳跃的外部因素,现在我们已经到目前为止,我们认为这是由 ADC 内部的某些因素造成的伪迹。

有人以前是否观察过这种行为? 是否有解决方案? 它确实会影响我们模块的性能。

此致、

Paul