主题中讨论的其他器件: ADS4128、 ADS4149

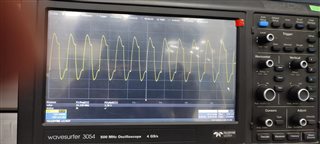

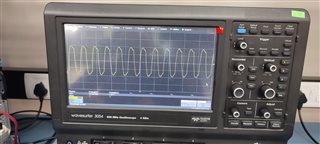

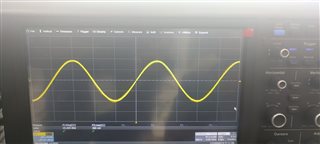

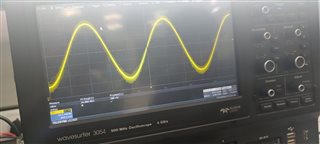

在我们的定制板中、我们使用的是 ads4129。 寄存器配置为 x"41C0"、x"3D80"、x"4208"、x"DF30"、x"0303"、x"4A01"、 x"2503"、x"2500"。 采样时钟为24MHz。 我们已在 FPGA 上捕获数据并在 MATLAB 中进行分析。 混叠后、预期的输出频率不会出现。 我们确保了 FPGA 捕获的输出和 ADC 输出(探测并检查 ADC 输出引脚的 MSB 位)完全匹配、因此没有故障。 那么、该问题的原因可能是什么? 对于基准、我已连接输入 clk、output_clk 和输入频率的输入 FFT 输出。