您好!

我在定制板中使用的是 ADS4149 ADC。 ADC 采样时钟由 FPGA 驱动。

采样频率(fs)= 24MHz

ADC 输入信号频率(Fin)= 328MHz

ADC 输入信号功率级别=-10dBm。

FPGA 器件型号:MPF200T

我将通过 FPGA 将 OCXO 时钟(24MHz)路由到 ADC、作为 FS。 我可以在 ADC 输出端看到8MHz。

问题1陈述:

现在、我将通过 FPGA 的内部 PLL 而不是 OCXO 生成相同的24MHz 时钟、并以 FS 的形式路由到 ADC。 ADC 输出本身不正确。 预计为8MHz、但仅存在 junks。

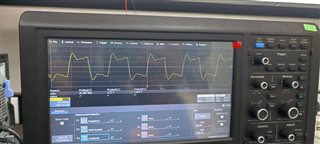

我已经用示波器探测了 ADC 时钟信号、可以在 OCXO 时钟和 FPGA 的内部 PLL 时钟之间做出以下改变。

OCXO 时钟的范围为-0.2V 至+1.5v、过冲为0.4v (附件 OCXO_AS_ADC_FS)

内部 PLL 时钟的范围为-0.3V 至+1.7V、过冲为0.5V

从 ADC 数据表中可以看出、LVCMOS 单端配置的时钟信号最大电压为1.8V。 我们使用相同的 LVCMOS 单端配置。

我可以看到内部 PLL 时钟超过1.8V。 请告诉我、问题是由于这个问题而发生的?

问题2:

ADC 时钟在 ADC 输入信号中耦合。 基波为328Mhz。 由于 ADC 时钟耦合、我们看到基频降低了352MHz、376MHz 和400MHz @23dB。

请提供建议以消除此耦合问题。

注意:此处附上了 ADC 部分原理图。