主题中讨论的其他器件: ADC128S102

您好!

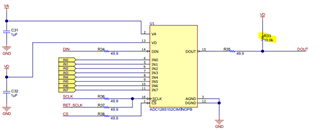

我有一个 ADC128S102EVM 板、我尝试使用 Microsemi 的 ProAsic3E 与 ADC 进行通信。

为此、我移除了电阻器 R42以使用外部 VA/VREF (在本例中为3.3V)、并添加了一根导线、以便使用 ProAsic3E 3.3V 为 VD 供电。 PHI 板未插入、我当前不使用它与 ADC 进行通信。 SPI 通信来自 ProAsic3E、并连接在 J26上。

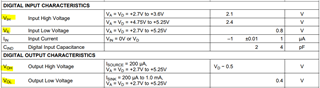

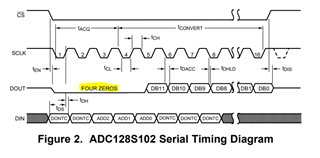

我的问题是、无论地址如何(介于 b'000'和 b'111'之间)、我都在 DOUT 上接收到 ADC 通道0的值、并尝试在 DIN 上发送。 但是、如果我在 CS 处于低电平时在 DIN 上发送逻辑1、则我得到 ADC 通道7的值。 但如果我只送了 b'111",情况就不是这样了。

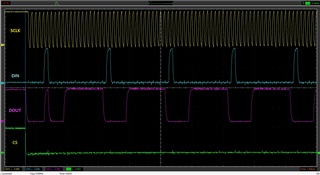

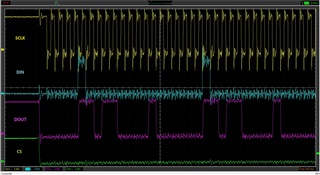

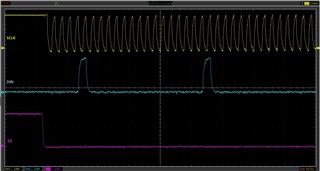

它看起来像是时序问题、但我已经使用示波器检查了控制信号、并且这些信号遵循 ADC128S102数据表中描述的协议。

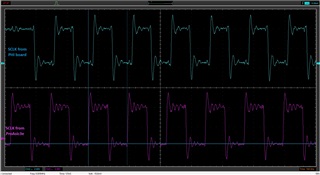

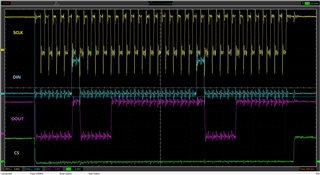

这是我随 FPGA 发送的用于读取 ADC 通道1的数据。 (我的探头位于 J26上)

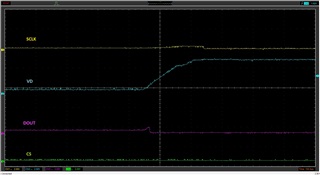

我已经检查了 VD、就是这种情况。

我首先 使用 PHI 板和 ADC128S102EVM GUI 测试了 ADC128S102EVM。 在本例中、我可以读取每个 ADC 通道、而不会出现任何问题。 因此 ADC128S102EVM 能够正常工作。

是否有任何想法、知道在哪里可能会出现问题?