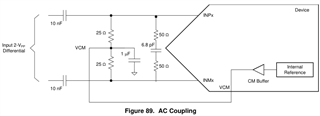

我找不到之前被问到的问题。 我要将 ADS52J90输入连接到另一个器件的100Ω 差分(Zdiff)模拟输出。 数据表图89如下图所示、但我不明白它为什么同时具有100Ω 和50Ω 端接。 我认为这既是用 VCM 端接50Ω 对、又显示了100Ω 端接(两者都没有必要)? 如果两者同时存在、则会导致阻抗不匹配。

数据表的图90 (直流耦合)仅显示了100Ω 端接。

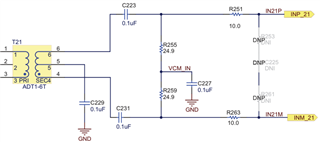

我已根据 EVM 原理图推导出了此设计、其中包括安装的50Ω 端接、因为它包含 ADT1-6T (1:1 50Ω)平衡-非平衡变压器:

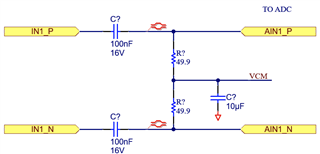

我基本上使用了 EVM 电路(没有50Ω 电阻器和6.8pF 电容器)、但针对我的100Ω Zdiff 系统将24.9Ω 电阻器更改为49.9Ω、如下所示(代表我的系统)。 这不是端接差分对并注入 VCM 的正确方式吗?