工具与软件:

您好

如果 ADC 内部数字滤波器的截止频率低于我的模拟抗混叠滤波器、这可能会导致问题(即抗混叠)。

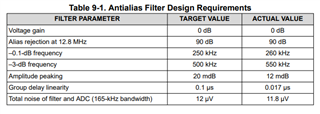

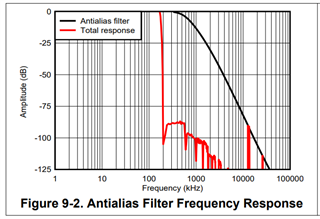

例如、我的模拟滤波器是一个截止频率为-3dB、约为20kHz 的四阶滤波器。 我想将 ADC 与高速模式宽带滤波器一起使用)。 由于某种原因、我可能需要在 OSR 256和 OSR 512之间切换。 我认为第一种情况应该不会有任何问题、因为截止频率匹配、但我想第二种情况不知道:

这个"中间"频带内的输入频率会发生什么情况? 如果我正确理解数据表、那么这个模拟滤波器的一个主要目的就是滤除 f_mod 位置的输入频率。 所以我认为这应该是好的,但我只是想确保它不会导致问题。

非常感谢

乔纳斯