请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:AFE11612-SEP 工具与软件:

您好、E2E:

这一调查适用于关键的长期太空飞行任务。

在 I2C 接口中用作 SCL 时、SCL/SCLK 引脚的额定最大尖峰抑制(TSP)为10ns 至50ns、具体取决于接口速度。

当 SCL/SCLK 引脚用作 SPI 接口中的 SCLK 时、AFE11612内的 SCLK 是否应用了任何尖峰抑制、如果是、抑制的最大尖峰间隔是多少?

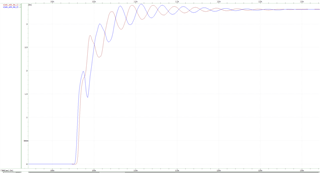

更具体地说,当在 SPI 接口中使用 SCLK 引脚时,可以容忍非单调上升沿和下降沿,我们的 SI 仿真显示 SCLK 上的一些非单调边沿,需要知道这是否会导致"时钟错误"?

谢谢!

-John