主题中讨论的其它部件:SN65DSI85

大家好,

我们在产品中使用LVDS显示器,我们希望将LVDS显示器与支持MIPI显示器的Qualcomm Snapdragon 820处理器连接起来。 为了将MIPI转换为LVDS,我们在设计中使用了SN65DSI85。

我们的用例是从处理器传输双分割DSI输出,即整个显示屏的半幅图像将传输到一个DSI 4通道端口,另一个半幅显示屏将传输到第二个DSI 4通道端口。 我们希望LVDS端的场景与LVDS1上的一个显示屏将显示完整图像的一半部分,而第二个显示屏将显示完整图像的剩余一半部分相同。

我已随案例附上寄存器设置,以下是我们的观察结果:

1) 我们可以在SN65DSI85的两个DSI端口的输入端接收DSI数据和时钟通道。

2) 我们无法在两个LVDS端口上接收LVDS信号。 一次只有一个端口工作。 我们希望两个LVDS端口同时工作。

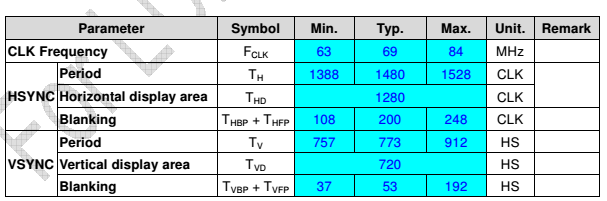

3) 显示屏的分辨率为720p@60fps。

4) LVDS单端口上的数据有时也不起作用,有时也起作用。

是否可以有人验证寄存器设置 并告诉我们需要使用的确切设置。