https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1189926/dp83869hm

器件型号:DP83869HMこんにちは、担当者様。μ A

DP83869HMについて下記の点を教えてください。μ A

弊社基板の回路構成 μ A

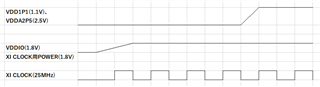

(1) DP83869HMの電源構成は、双电源 Configurationで構成してます。

また、VDD*端子には下記の電圧を供給しています。

・VDD1P1:1.1V

・VDDA2P5:2.5V

・VDDIO:1.8V

・VDDA1P8:オープン μ A

(2) XI端子については、水晶発振器を使用し供給しています。

また、水晶発振器は、VDDIOと同じ電源で1.8Vを供給しています。μ A

また、XO端子は「打开」です。

【質問】μ A

・電源投入シーケンスについて確認させてください。μ A

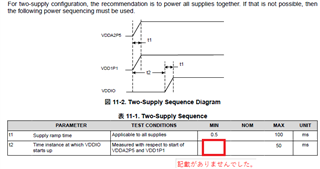

データシートには、μ A

「2電源構成の場合、すべての電源をまとめて電源を入れることをお勧めします。μ A

それが不可能な場合は、次の電源シーケンスを使用する必要があります。」μ A

と記載があります。μ A

下図では、「VDDA2P5、VDD1P1を投入」→「VDDIOの電源投入」の順序にみえます。

ただし、VDDIOについては、MIN値についての記載がありませんでした。μ A

上図についてですが、VDDIOがマイナス側になるのは、問題はありませんか?

下記の投入順序でも問題はありませんか?