主题中讨论的其他器件: THVD1520

您好!

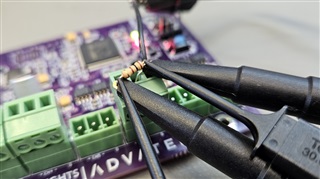

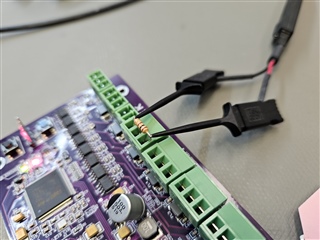

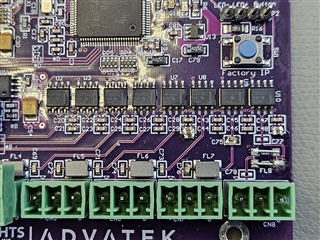

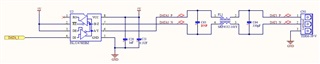

我们在产品中仅将 THVD2450用作 RS485驱动器。 原理图如下所示。 使用共模扼流圈(FL1)来消除共模噪声。 两个电容器(C63和 C64)用于延长信号上升时间、以实现 EMC 目的。 输入信号(数据1)是3.3V 电平、具有各种频率。 在我们的测试中、在两个差分信号之间的连接器(CN1)上添加了一个端接电阻器。 直接在连接器上测量信号。

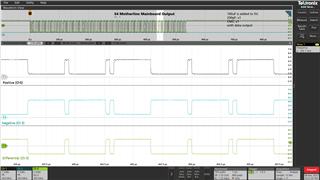

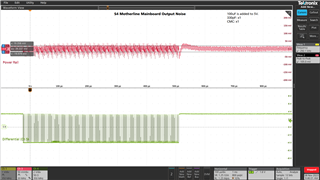

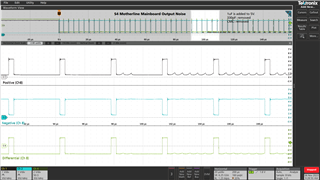

我们在差分信号上发现了一些噪声、也在正负信号上发现了一些噪声、如下面的第一张图所示。 与此噪声相关的一些有趣现象是:

1.噪声只会发生,或者我们可以说在大约25个正脉冲后变得更加明显。

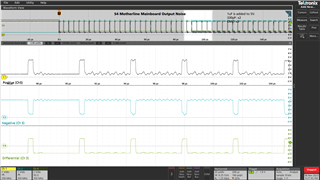

2.降低信号频率时,没有发现噪声,如下图所示。

3.将 THVD2450替换为 THVD1520 (和其他制造商提供的另一个 RS485收发器)后,无论信号的频率如何,都不会发现噪声。

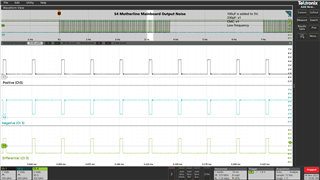

为了排除差分总线上共模块和电容器产生的影响、我拆除了它们并短接共模扼流圈的焊盘。 差分信号上仍然存在噪声、但有些不同。 现在看来只有正信号有一些噪声、负信号看起来还是比较"干净"的。 波形如下图所示。 这肯定会导致差分信号上出现噪声。

我还尝试在 THVD2450的电源轨上添加更多的大容量电容器和去耦电容器、但这对降低噪声没有帮助。

我的问题是:

THVD2540支持比 THVD1520更高的数据速率。 是否是在使用 THVD2450时更容易发现噪声的唯一原因?

2.我们发现只有在25个正脉冲后才会有噪声。 它是否与 THVD2450的某些特性相关?

3.虽然噪音的幅度似乎 不太可能影响其功能,我们是否有任何建议的解决方案可以尝试让噪音消失?

谢谢!