请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

常见问题解答:逻辑和电压转换 > 输入参数 >>电流常见问题解答

简短答案:对于具有总线保持电路的器件、不建议使用外部上拉/下拉电阻器。

说明:

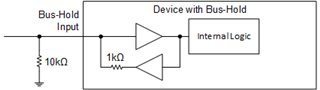

只要总线保持器处于与电阻器电源相反的状态、上拉或下拉电阻器就会产生一个带有总线保持电路的分压器。

例如:

对于典型的总线保持电路、输出电阻约为1k Ω。 如果输入端有一个10kohm 下拉电阻器、并且没有以其他方式主动驱动线路、则可能存在两种状态:

(1)总线保持电路处于低电平状态、没有问题。

(2)总线保持电路处于高电平状态、现在输入电压被下拉至~0.9 * VCC。

如果您不关心输入处于何种状态、那么#2不是什么大问题、但如果您打算将下拉电阻器置于低电平状态、那么您可以看到它不起作用、除非电阻器非常小(即小于1k Ω)。

如果是这种情况、最好不要使用总线保持。

您可以在本应用手册 第6节中深入阅读有关总线保持电路及其工作原理的详细信息:慢速或浮点 CMOS 输入的影响。