主题中讨论的其他器件: TXU0101、 TXU0104、 SN74AHC1G125

大家好、

我们的客户使用的是一个控制器和两个响应者、他们具有 SPI 接口、并希望澄清 SPI 引脚的连接。 根据我们的客户、

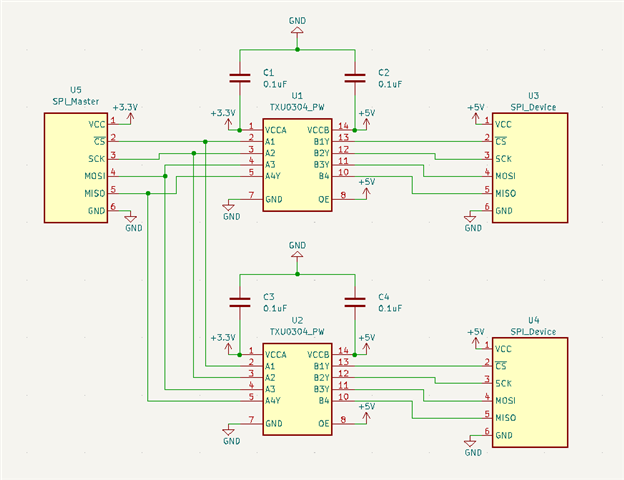

我正在设计一个使用 TXU0304芯片将 SPI 总线信号电平转换为多个 SPI 外设的电路。 每个外设都有一个单独的 TXU0304芯片、并连接到单个 SPI 主器件。 当 CS 信号失效时、每个 SPI 外设将 MISO 信号置于高阻抗状态。 我的问题是、我应该如何处理 TXU0304芯片到 SPI 主器件的 MISO 输出? 当相应的 SPI CS 信号取消置位时、是否需要使用 TXU0304上的 OE 引脚将所有输出置于高阻抗状态? 我可以将 OE 引脚连接到 CS 吗? 对于这种类型的拓扑、是否有推荐的方法?

他还补充说:

随附的是我目前的原理图。 我担心、虽然当 CS 置为无效时、每个 SPI 器件上的 MISO 引脚被置于高阻抗状态、但相应 TXU0304芯片上的 A4Y 引脚将不会处于高阻抗状态、从而导致总线争用。 是这样吗? 我是否应该将 GPIO 引脚连接到每个 TXU0304上的 OE 引脚、以便在 CS 置为无效时将其强制为高阻抗?

我知道、在多个 SPI 器件中、每个 CS 引脚应连接到控制器的单个 I/O。 似乎更好的配置是将 SCK、MOSI、U3和 U4的 MISO 并联、移除 U2并 为控制器的另一个 CS 引脚添加 TXU0101到 U4的 CS?

或者、如 上图所示、使用两个 TXU0304、将 U1的 BY1连接到逆变器、然后连接到 U1的 OE (U2采用相同的配置)、并将 U1和 U2的 A1分离、将防止 U3和 U4的 MISO 之间发生数据冲突。

您能否确认哪种解决方案适用?

此致、

Danilo