主题中讨论的其他器件: SN74AUC1G17

大家好、

我的客户正在使用我们 的 SN74LVC1G17电平位移来驱动12通道 SDI IC。

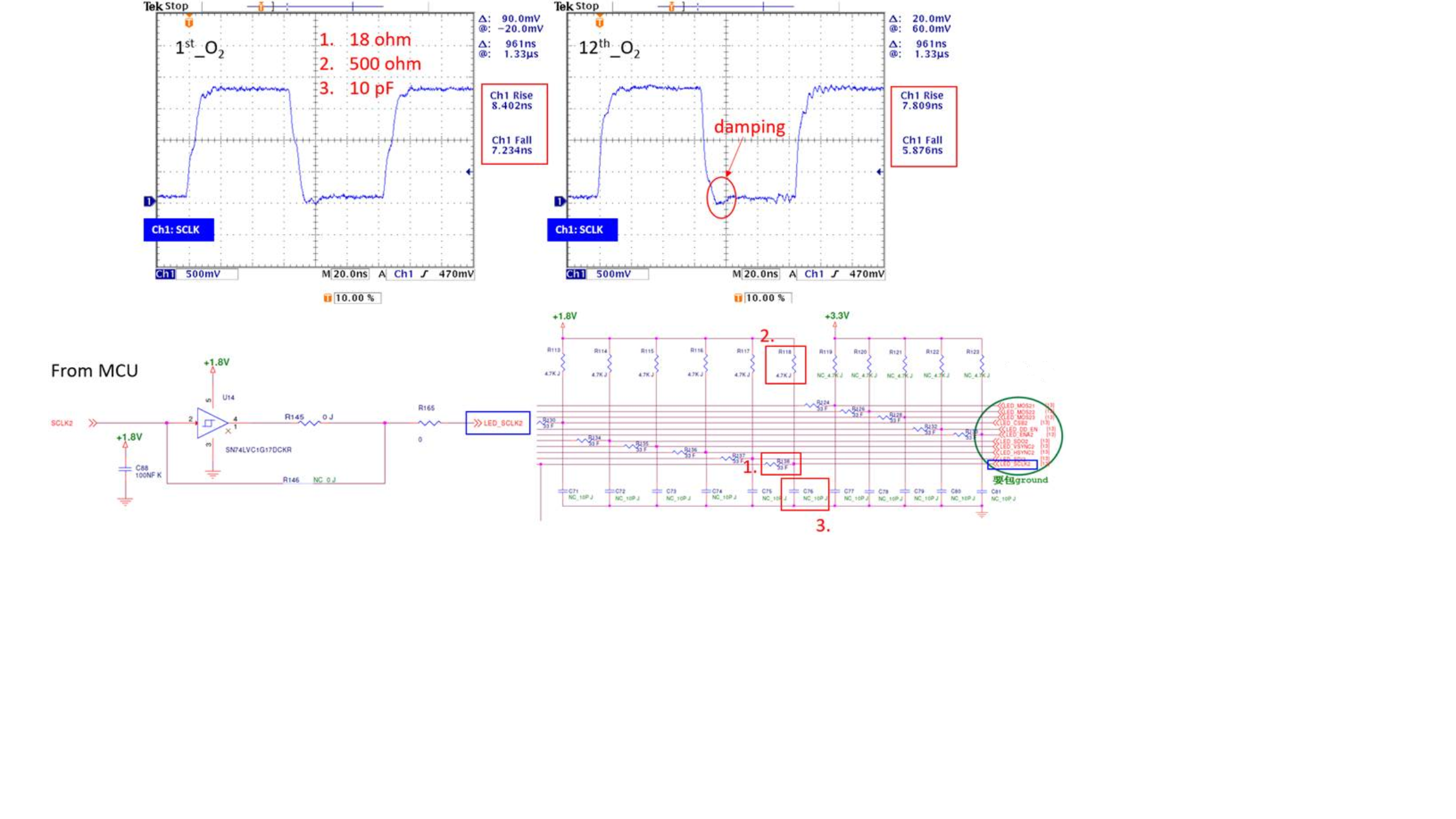

原理图和输出波形如下所示。

他们使用了两种情况。 它们的不同之处在于 在原理图中使用不同条件的开漏电阻器(2)、串联电阻器(1)和并联电容器(3)。

第一个:1. 串联电阻= 18 Ω、2. 开漏电阻器= 500欧姆、3. 并联电容器=10pF

结果: 12通道中最差的上升时间= 8.402ns

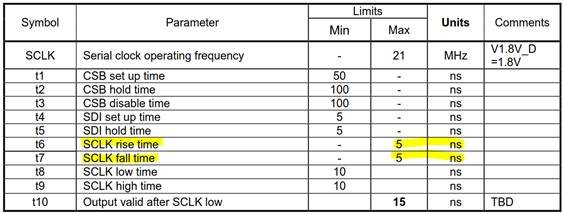

下一级 IC 不允许使用该功能。 该规格仅为5ns

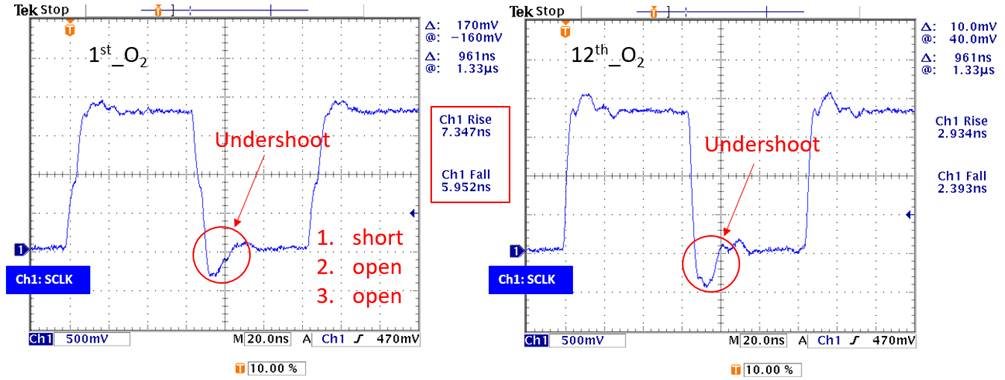

第二个:1. 串联电阻=短路、2. 漏极开路电阻器=开路、3. 并联电容器=开路

结果: 上升时间已经改善、但它将具有下冲行为

可以帮帮我吗? 如何改善下冲行为? 是否为测量误差? 探针的输入电容约为8pF。 电平位移 与 SDI IC 之间的布线约为8000mil。