大家好、

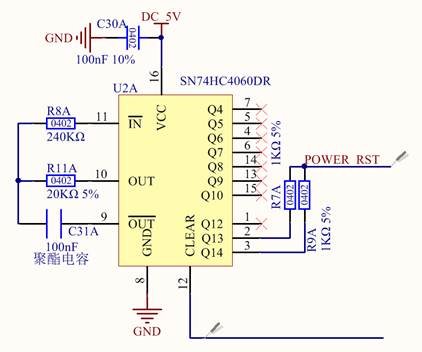

我的客户正在使用 SN74HC4060设计系统、以实现如下所示的看门狗功能。

通常连接 R7A (1k Ω)或 R9A (1k Ω)以获得输出。

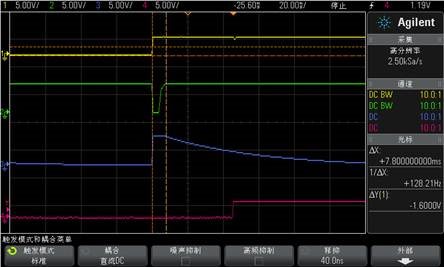

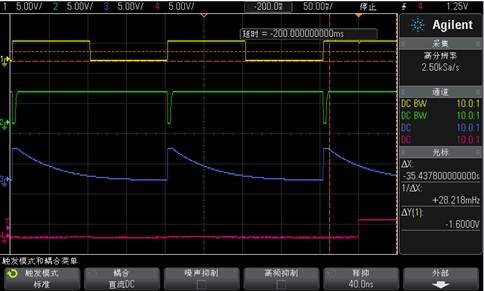

但是、在某些情况下、它们犯了一个错误、将 R7A 和 R9A 连接在一起。 然后、它会导致 RST 错误地具有高输出、即使在正常的进给操作下也是如此。 您可以按如下所示检查波形。 蓝色线是 SN74HC4060的 PIN12波形、而红色线是电源 rst 输出。

我们发现、如果将两个电阻器连接在一起、问题可能会再现为100%。

那么、问题是、如果 R7A 和 R9A 同时连接在一起、 是否有可能对 SN74HC4060器件造成物理损坏?