主题中讨论的其他器件:SN74AHC1G09、 SN74HCS09

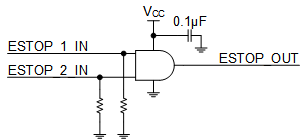

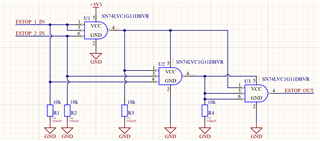

我的电路是安全系统的一部分。 当 ESTOP_1_IN 和 ESTOP_2_IN 都为高电平时、ESTOP_OUT 也应为高电平、具有基本与门功能。

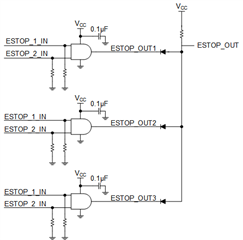

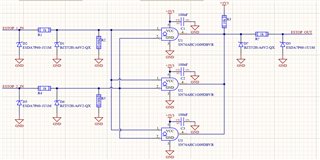

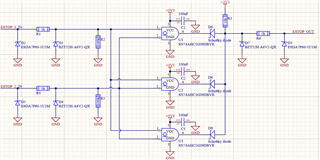

为了降低该系统不安全故障的风险(例如、将输入/输出短接到封装/芯片内部的3V3或输出驱动器卡在高电平)、我决定再添加2个与门。 这样、至少2个和门需要以不安全的方式发生故障、才能在 Estop_out 处获得不安全的状态。 为了实现这一点、我将使用1和2与门的输出为第2和3与门供电。

我的问题是:

此设计中是否存在我要忽略的任何风险?

我到目前为止想到的风险:

风险1:输出端压降

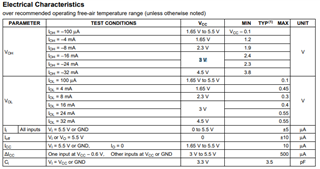

SN74LVC1G11的数据表显示了 VCC 和输出在不同电压和负载下的压降。 这里的风险是、级联与门会导致在第3个与门之后的 Estop_out 上的电压过低。 我不希望这里出现问题、数据表显示了在 VCC=3V、负载为24mA 时下降0.7V。 在我的情况下、负载将会低得多、因为我仅为其他与门供电(几 uA)、并使用10kOhm 电阻器进行下拉。

风险2:下拉电阻器故障

当其中一个下拉故障时、可能会使与门输入卡在 GND 或悬空。 在我的应用中、对 GND 短路将被视为"安全"。 但是、悬空状态不安全、因为与门的行为可能不稳定。 为此、我选择使用 MELF 电阻 器、以实现更高的稳定性、耐湿性和工作温度。

诸如 tombst立 石之类的生产错误仍然可能导致输入浮动、但我相信我们的生产机构可以通过 QC 来解决这一问题。