请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:DRV8343-Q1 您好,

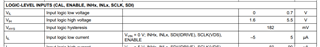

DRV8343SPHPRQ1的数据表指出SCLK引脚存在182mV (典型值)的输入逻辑滞后。

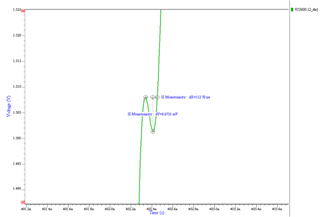

在这种情况下,我们想确认SCLK波形中的以下非单耳性是否不会影响SCLK的正常操作。

上述非单耳性的存在时间为6.673mV,且持续时间为112.7ps。 我们预期此波形失真将被输入滞后(AS 6.673mV < 182mV)拒绝,这将防止错误切换。

请确认。

此外,请告知我们是否存在输入滞后的最低规格。