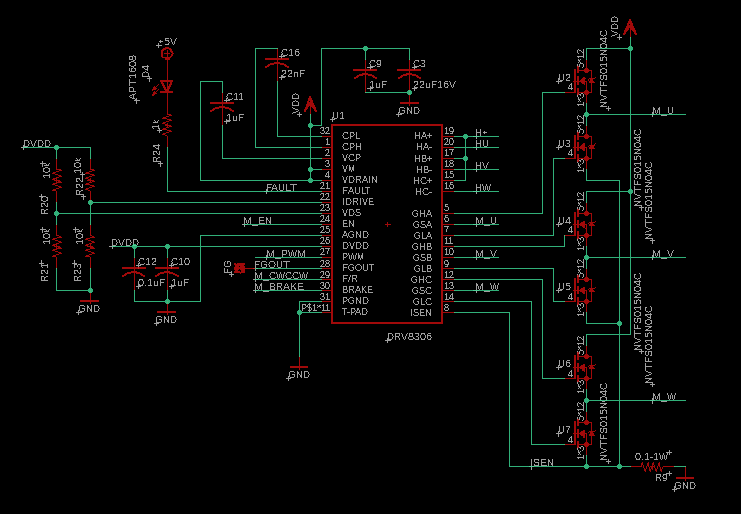

主题中讨论的其他器件:CSD18514Q5A

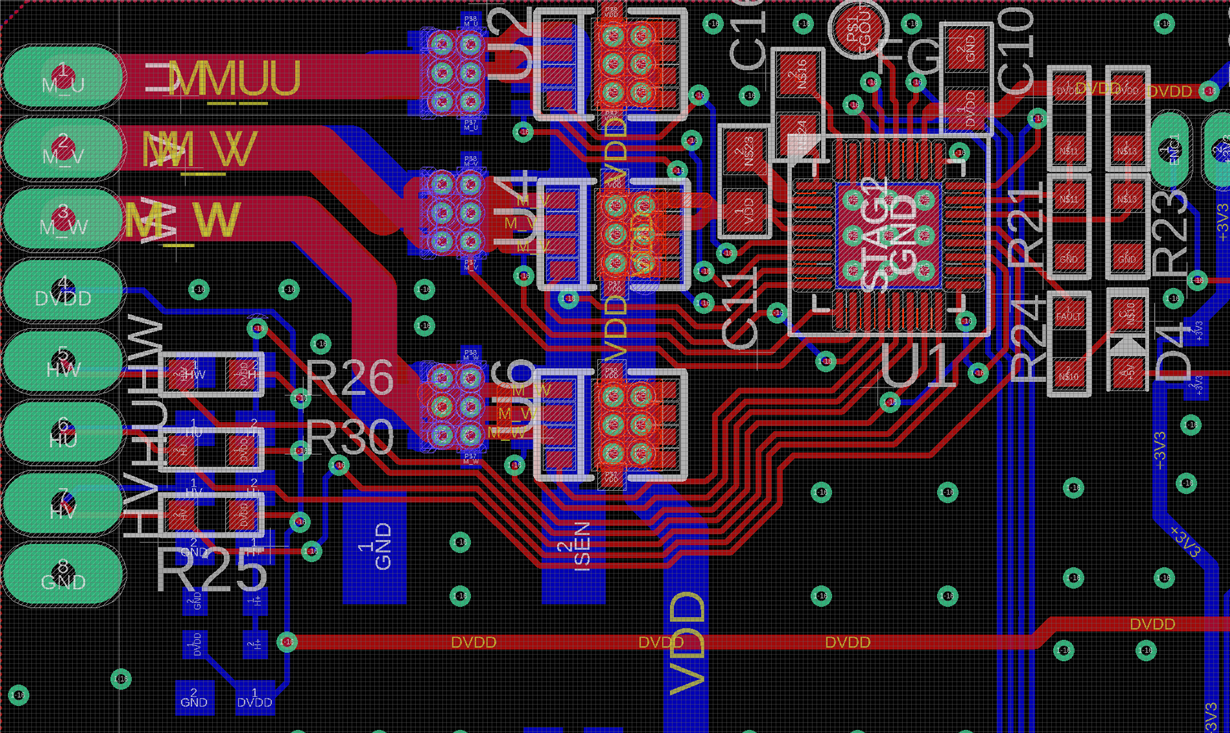

我们对 BLDC 电机控制板进行了原型设计。

以下各点似乎正常。

・通过改变 PWM 引脚实现速度控制。

DIR 引脚上的・正向/反向旋转控制。

・制动销处的制动控制。

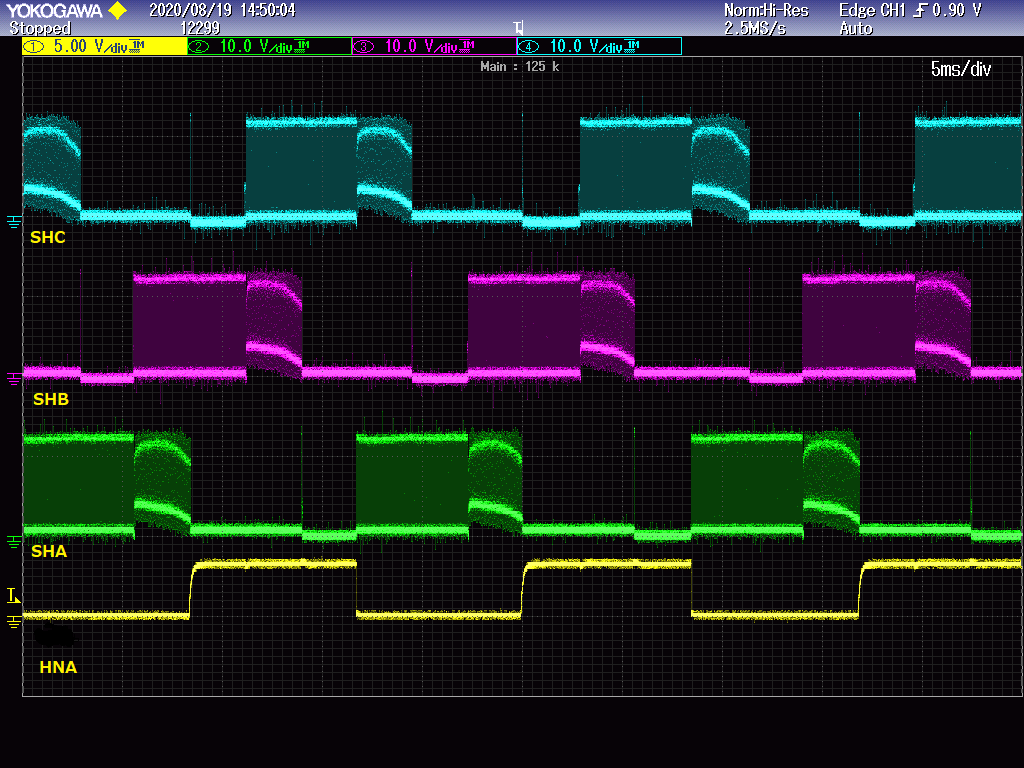

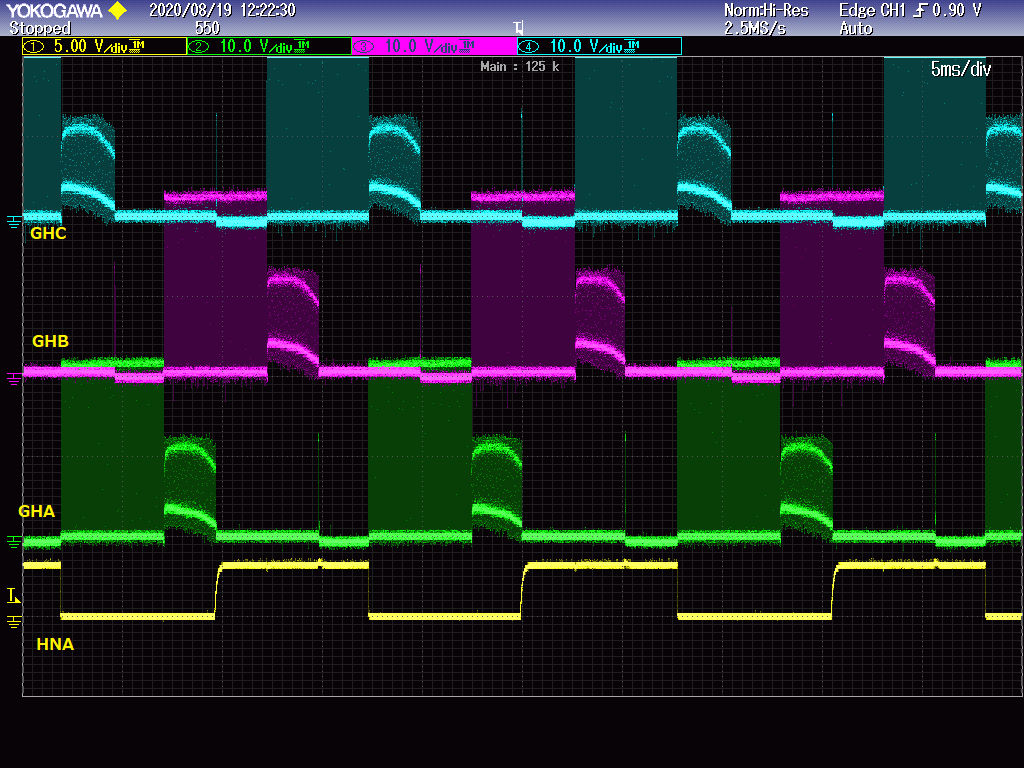

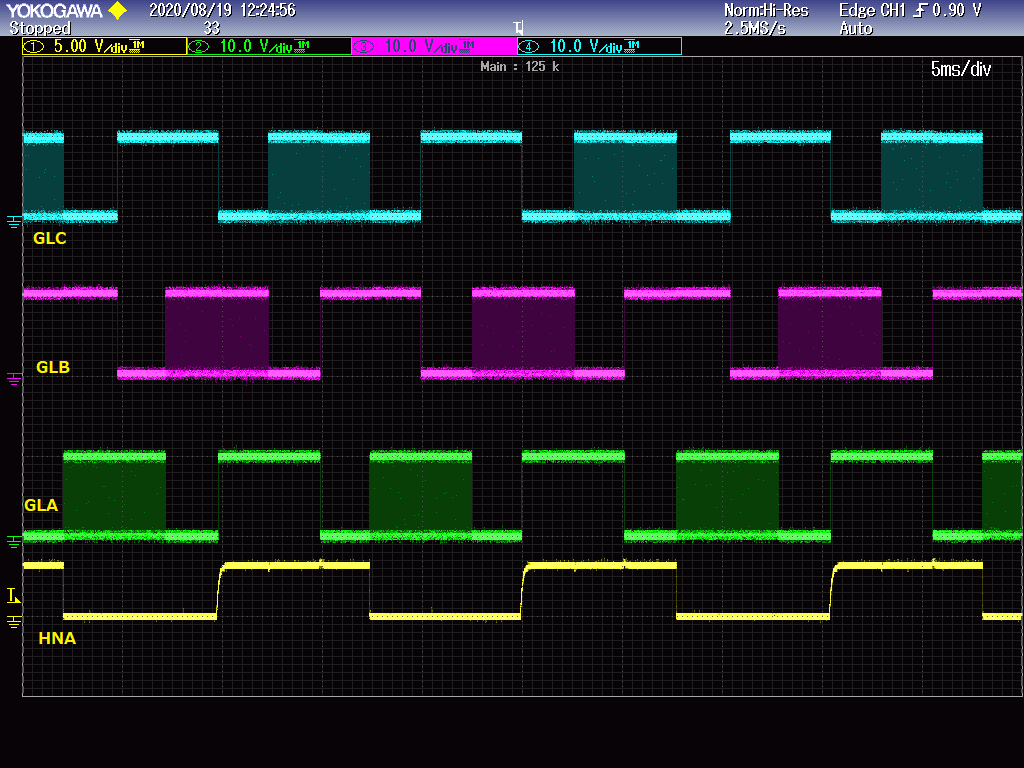

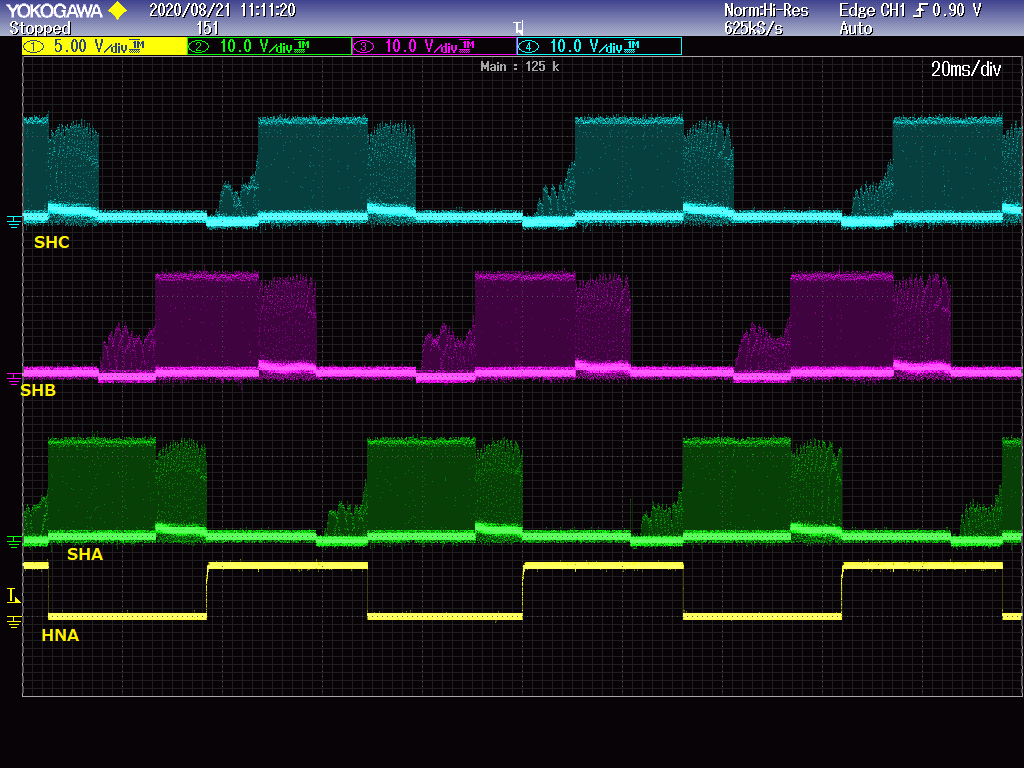

但是、电流和热量产生了很大的影响、因此当我检查波形时、它看起来像所附的图像。

每个相位中 FET 输出的 PWM 波形的左侧是 GND 电平。

当旋转反转时、PWM 的右侧变为 GND 电平。

我调节了 IDRIVE 端子、但它没有改变。

FET 使用了 ONSemiconductor 的 NVTFS015N04C。

https://www.onsemi.jp/PowerSolutions/document/NVTFS015N04C-D.PDF

我怀疑与 FET 的兼容性、因此我尝试了另一个 FET SiRA18BDP、但它没有改变。

https://www.vishay.com/docs/77143/sira18bdp.pdf

当 GLA、GLB 和 GLC 从 H 变为 L 时、尽管栅极为 L、但 FET 似乎出现故障并导通

当 GLA、GLB 和 GLC 从 PWM 变为 L 时、它似乎正常运行。

我想知道是否有任何点可用于选择检查点或 FET。

提前感谢您。