“线程”中讨论的其它部件: ABS, TPS7A85, TPS7A84

您好 TI 团队,

我对 TPS7A8300有疑问

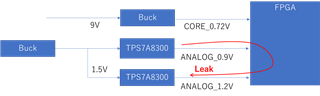

我们有上述的电源轨。

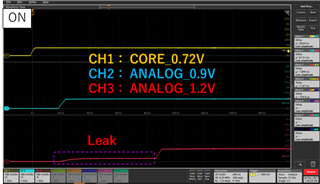

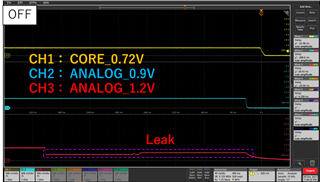

首先,1.5V 是降压转换器的输出,然后在模拟1.2V 之前启用了模拟0.9V,并且 FPGA 在模拟1.2V 启用之前泄漏了电压。

因此,我们的打开和关闭波形如下所示。 模拟1.2V 有一些泄漏,但不超过0.9V。

我的问题是:

这种泄漏是否会在可操作性和可靠性方面对模拟1.2V LDO 产生任何影响?

由于设计限制,我们不想添加额外的负载开关或更改 LDO。

此致

Naim