您好!

我们在具有高电容负载的电路中实现该 IC、Vin 高于20V 的额定 Vgs 阈值。

输入电压最大为60V。

RO 目前为18k

如果发生故障情况、Ro 会导致 OUT 引脚被拉至 GND+二极管压降、而 Vout 仍为50V+。 这会导致 MOSFET 断开、因为 Vgs= Ro+内部二极管上的压降。

是否有任何缓解此问题的方法?

提前感谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我们在具有高电容负载的电路中实现该 IC、Vin 高于20V 的额定 Vgs 阈值。

输入电压最大为60V。

RO 目前为18k

如果发生故障情况、Ro 会导致 OUT 引脚被拉至 GND+二极管压降、而 Vout 仍为50V+。 这会导致 MOSFET 断开、因为 Vgs= Ro+内部二极管上的压降。

是否有任何缓解此问题的方法?

提前感谢!

感谢您的回答。 公式仅显示 Ro min、并平衡 Vdth I 调整 Ro 与 Rs 之间的关系。 这就是我提出18k (已经设置了 Rs)的方法。

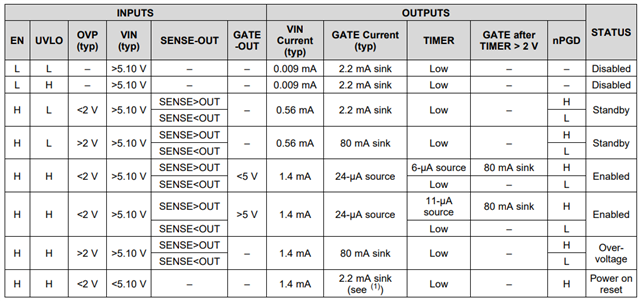

我可以先找到所需的 Ro 值、然后找到 Rs 值。 因此、当 Ro 约为200欧姆时、Ro 上的电压将低于额定 Vgs 并保持 MOSFET 安全、但 Ro 和 IC 的80mA 灌电流电路将消耗相当多的功率。 这可以通过一个电阻器来处理某些功率(1、28W)、但 IC 中的功率耗散仍然太大(3.52W)。 如果我将其增加到

当我谈论故障条件时 、我是指 IC 尝试灌入80mA 电流的情况。(但也适用于 Ro 非常大>9k Ω 时的2.2mA 灌电流。

我还没有捕获任何曲线、只是用 mm 验证了 Vgs、并通过查看 IC 的方框图来了解正在发生的情况。

我在这篇帖子中的两个目标:

可能会找到一个可以节省 MOSFET (和 IC)的电路。

如果这个问题是我认为的:在"大负载电容部分"中添加一些有关电压> Vgs 额定值的注释。