你好!

LM5123 (XLM5123)的预量产样片提供了以下观察结果。 如果这是一个已知问题、并且已通过生产版本修复、请告知我。

在测量我们的设计时、我们发现低侧晶体管的栅极出现异常行为 、该晶体管连接到 IC 上的"LO"。

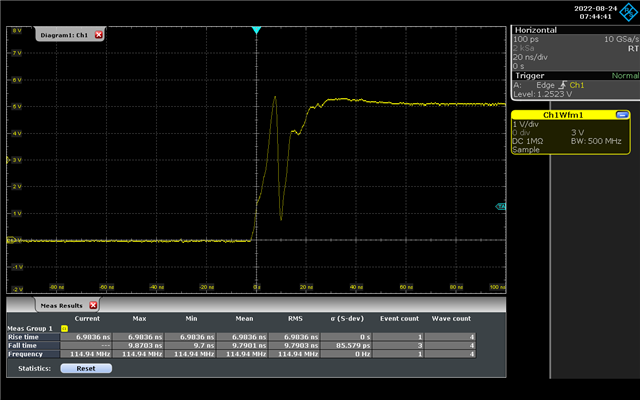

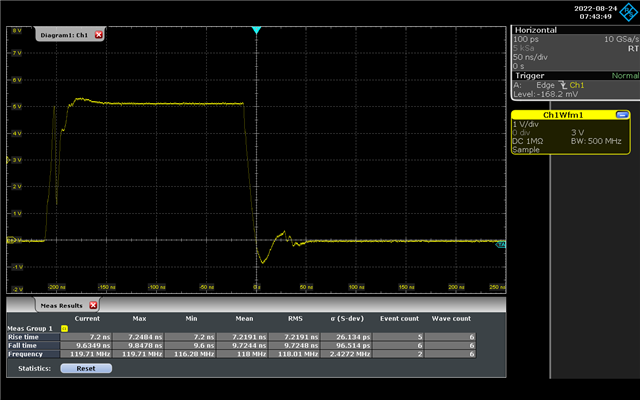

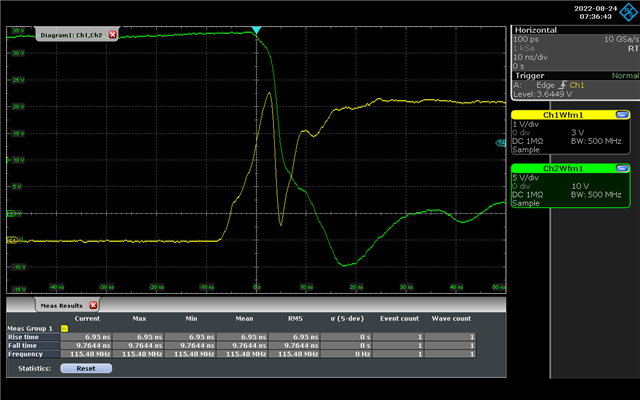

在最初为栅极供电时、栅极驱动器电压似乎会击穿。 以下示波器测量是在低侧 FET 的栅极和源极(GND)之间进行的、探针上有一个非常短的接地引线。

上升沿的特写:

低侧 FET 的完整周期:

下一幅图像以绿色显示开关节点以供参考(可能存在的值不准确、因为接地基准位于另一个探头上)

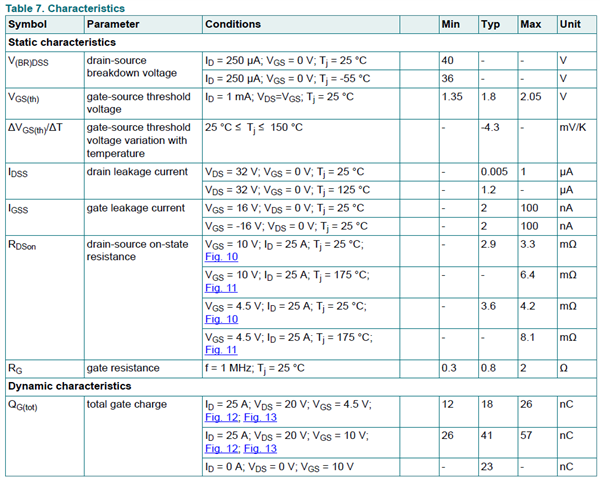

我们使用的是 NExperia PSMN3R2-40YLD、它具有以下特性:

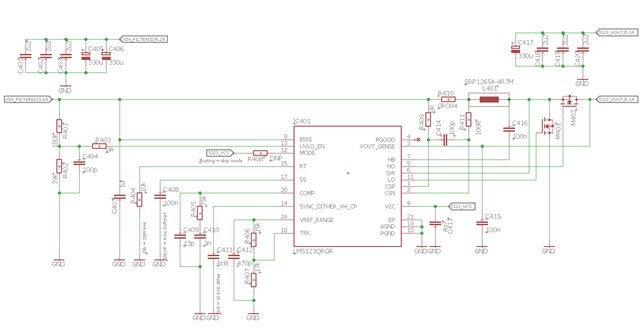

这是我们的原理图

低侧 FET 相对较热、我们假设这是因为栅极充满电需要很长时间、因此 FET 处于线性模式的时间比需要的时间长。

您能向我们提供有关此行为的任何信息吗? 我们是否可以通过任何方式来提高性能?

此致

Felix