主题中讨论的其他器件: UCC27511、 CSD18510Q5B、 CSD18536KTT、 CSD18512Q5B、 CSD18563Q5A、 CSD19505KTT、 CSD19505KCS、 UCC27525

尊敬的专家:

我无法在 pspice 中仿真该电路、该 MOSFET 电路是否正确、如果错误、请帮助我构建更好的电路。

CSD18542KTT

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的专家:

我无法在 pspice 中仿真该电路、该 MOSFET 电路是否正确、如果错误、请帮助我构建更好的电路。

CSD18542KTT

您好、Naveen、

再次感谢您关注 TI FET。 要回答您的问题:

此外、可能需要调整栅极电阻器以获得 FET 所需的上升和下降时间。 100欧姆可能太大、具体取决于您的要求。

最后、您能否与我分享您的 PSpice 仿真?

谢谢、

John Wallace

TI FET 应用

您好、Naveen、

您的原理图看起来不错。 然而、40A 时的功率耗散将超过此器件的能力、最大功率约为2.5W TJ = 25°C 时的导通损耗为40A x 40A x 14.5mΩ Ω= 23.2W。 有关 TI FET 功率耗散能力的更多信息、请参阅此技术文章。 您将需要为此应用选择导通电阻较低的 FET。 请看一下 CSD18536KTT、这是 TI 在 D2PAK 中具有最低导通电阻的 FET。 您可能还会考虑采用5x6mm SON 封装的 CSD18510Q5B 或 CSD18512Q5B。

此致、

John

您好 Naveen、

在 VGS = 10V 且 TJ = 25°C 时、CSD18563Q5A 的最大导通电阻为6.8mΩ Ω 40A 时的导通损耗为10.88W、不包括导通电阻的正 tempco (请参阅数据表中的图8)。 5x6mm SON 封装在多层 PCB 上的布局良好时、最大功耗约为3W。 您可以并联 FET 以减少传导损耗、并在表面积更大的多个器件上分散功率耗散。 采用这种方法时、导通损耗会通过并联 FET 的数量来降低、每个器件中的耗散是总功率除以并联 FET 的数量。 例如、如果并联两个 FET、则总导通损耗降低50%、每个器件将消耗50%的总导通损耗。 40A 时、总导通损耗为5.44W、而在每个 CSD18546Q5A 中、总导通损耗为2.72W。 栅极驱动和开关损耗会增加、但电机驱动器通常以较低的频率(大约20kHz)进行开关、传导损耗占主导地位。

谢谢、

John

Naveen、

感谢您的参与和对 TI 器件的兴趣! 我叫 Aaron Grgurich、是 UCC2752X 栅极驱动器系列的应用工程师。

----

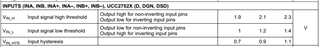

是的、如果 UCC27525的输入引脚由0V 至3.3V 的信号驱动、这将起作用。 数据表的第7.5节对此进行了概述。

----

希望这能解答您的问题! 如果是、请按绿色按钮;否则、请随时跟进!

谢谢、

Aaron Grgurich

Naveen、

抱歉、我忘记再次查看原理图了... 在总线电压为+48V 的情况下、您不能将此栅极驱动器与此处的 PMOS 搭配使用。 我建议使用 NMOS MOSFET。 NMOS MOSFET 的开关速度更快、并且导通的 R_DS 也比 PMOS 小(一般经验法则)。

如果您切换回 NMOS 设计、我仍有设计建议。

----

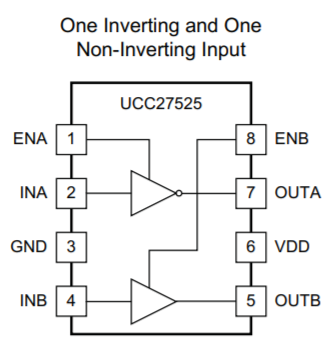

请注意、UCC27525的 INA 是反相的、INB 是同相的。 请确保这是您想要的(这对我来说似乎很好)

以下是我对该设计的评论:

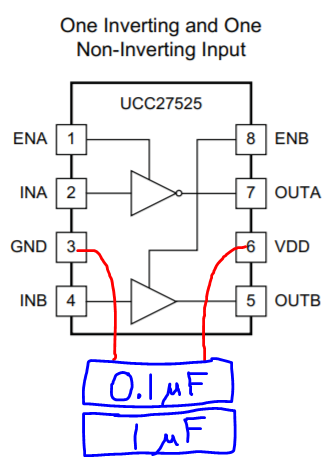

1)关于 V_DD 电容旁路、请参阅数据表的第8.3.1节。 应将100nF (0.1uF)电容器尽可能靠近 IC 放置、并联100nF 的1uF 电容器。 请参阅下图、了解如何布局电容器。

2) 2)根据 系统的噪声大小、 您可能需要进行输入信号滤波。 至少应将低通滤波器的放置架放入输入端 (放置架将是0欧姆的短路电阻器、不会装入电容器)。 如果您最后填充了低通滤波器、请勿放置大于100欧姆的电阻器和大于200pF 的电容器。)

3) 3) 将 INB 接地也许不是一个坏主意、但它不是必需的(因为它未被使用)。

4) R4应从功率 MOSFET 的栅极到源极(在您的原始原理图上是正确的)

----

很抱歉、您的 PMOS 问题缺少原理图、但我希望以上内容能为您提供帮助。

----

我希望这能回答你的问题。 如果是、请按绿色按钮;否则、请随意跟进。

谢谢!

Aaron Grgurich