主题中讨论的其他器件:LM74502-Q1、 LM74502、 LM74502H-Q1、 LM74502H、

大家好、团队、

我们将尝试评估 LM74502-Q1作为过压保护。 通过在 Q1 EVM 上测试 OV 截止行为、我们可以看到以下行为。 它看起来不是预期行为、到目前为止、调试不能提供任何有关根本原因的线索。

- OV 阈值设置为36V

- 从高于36V 的正常运行状态转变为预期状态、输出关闭

- 将 Vin 减小到36V 以下会提供我们在示波器屏幕截图中看到的行为

- 将 Vin 进一步降至28V 以下、行为再次如预期那样、输出开启

到目前为止、在没有浪涌电流控制的情况下进行了测试、并且最初的行为还可以。 现在、观察到这种行为后、仅为浪涌电流控制添加 RC 即可解决"问题"。

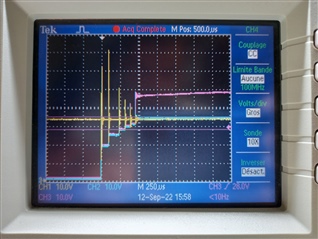

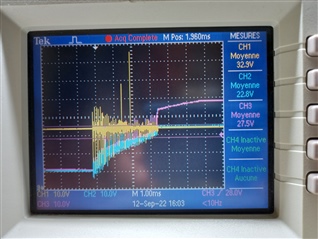

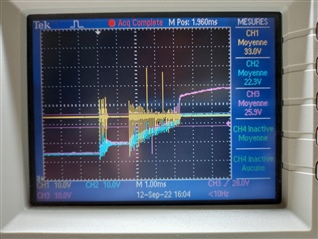

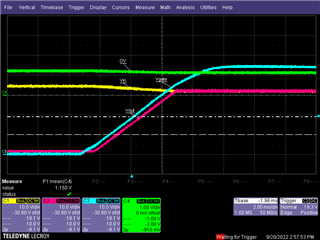

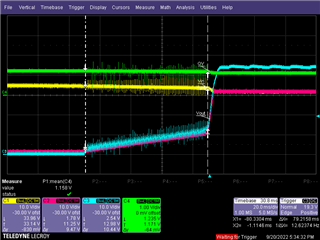

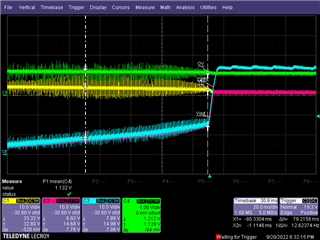

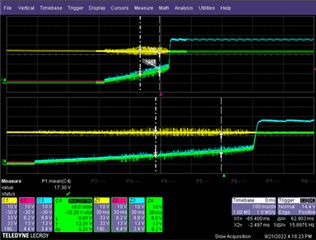

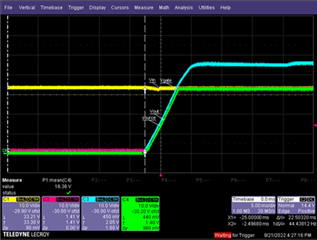

附加了一些示波器图。

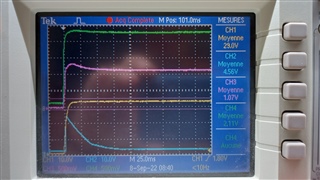

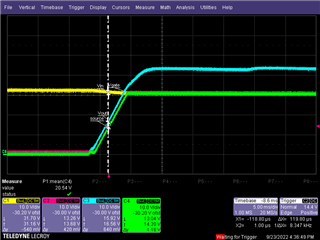

20220906_172210.jpg、其中黄色= VIN、蓝色= Vout、紫色= VGate

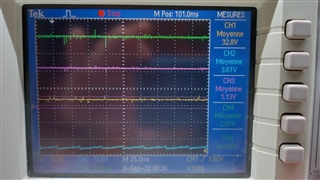

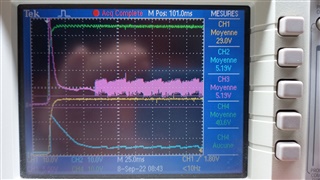

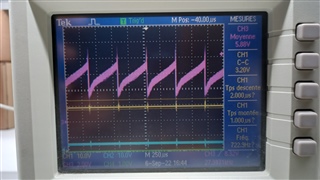

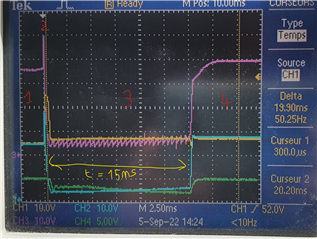

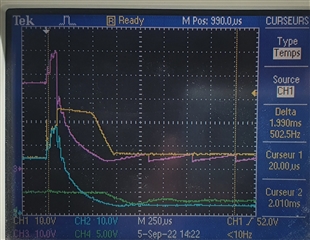

MicrosoftTeams-image (8).png、MicrosoftTeams-image (9).png 是与映像(8)相同的测试、但重点关注状态1至3。

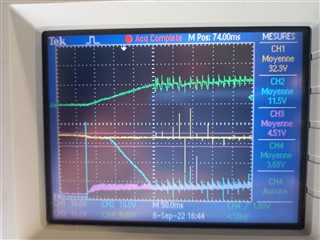

黄色= VIN、蓝色= Vout、紫色= VGate、绿色= 5V 电路板电源

1 =初始状态

2=激活 OV 保护的脉冲2b

3=未定义状态、Vout 在4V 左右、Vgate 在奇怪的电压下

4=产品恢复到初始状态、可能是因为 Vin 刚好低于阈值、但恢复时间很长。

您能不能帮助我们了解这种现象:

- 确保我们确定好的根本原因

- 建议的纠正措施是正确的

- 建议的纠正措施是明确定义的

此致、

维克托