您好!

我们正在智能电池设计中使用 BQ7692003电池监控器芯片。 我们构建了一款试验台、可根据标称保护阈值和延迟以及电池监控器数据表中列出的容差来测试每个 PCB 触发器上的芯片电压和电流保护。 过压 (OV)、欠压(UV)和放电短路(SCD)保护功能似乎 符合预期、但过流放电(OCD)保护的触发时序有时比预期更长、并导致偶发测试故障。

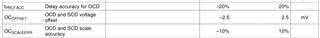

我们已经运行了一系列实验、下面是我们找到的内容。 对于以下所有情况、BQ76920配置如下:8mV OCD 保护 阈值(使用1m Ω 分流电阻器、即8A)、8ms OCD 保护延迟。 数据表建议所有延迟选项的容差为+/-20%、因此、对于标称值为8ms 的最低 OCD 延迟设置、我们期望在施加高于8A 阈值(+容差)的电流后、OCD 保护在6.4和9.6ms 内触发、 或6.5到9.7ms 之间、以考虑 FET 和 FET 驱动器延迟。

-

施加大于11.3A 的放电流9.7ms 会导致 OCD 触发成功率介于70%和80%之间

-

在9.7ms 内应用>16A 会导致~80%的成功率

-

在11ms 内应用>11.3A 会导致~90%的成功率

-

在20ms 内应用>11.3A 会导致~100%的成功率(测试无法完成、因此仅隐含此数字)

放电电流幅值和时序通过精密霍尔传感器电流探针验证。

请帮助我理解上面列出的观察结果。 我们是否误解了数据表中列出的容差范围? 我们在分析中没有考虑到任何隐藏因素。

提前感谢您、此致、