尊敬的主席/女士,您好。

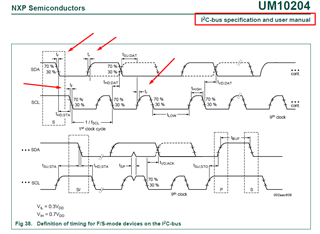

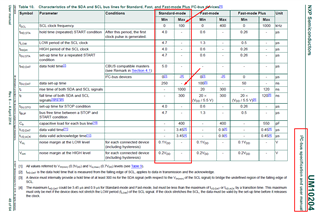

根据 LP5562规范[1]、最大的 SCL/SDA 上升时间要求为300nS (第6页的表6.8)、与针对快速模式(400kHz 时钟)的 I2C 标准[3](第48页的表10)所述的相同。 但我使用的是高达100kHz 的标准模式(在本例中为90kHz)、标准模式(100KHz 时钟)的标准[3]要求是1000nS。 300nS 要求是否仍然表示标准模式(100kHz 时钟)? 标准[3]中描述了标准模式的上升时间要求。

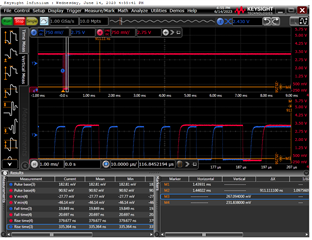

请注意、我正在测量上一线程[2]中描述的上升时间、10%到90%、这与图38第50页中描述的标准[3]不同。

[1] https://www.ti.com/product/LP5562

[2] https://e2e.ti.com/support/power-management-group/power-management/f/power-management-forum/1021633/lp5562-rise-time-and-fall-time-of-i2c

[3] https://www.nxp.com/docs/en/user-guide/UM10204.pdf

[4]