您好!

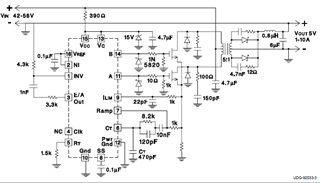

我正在开发一种使用旧部件 UC1825BJ/883B 的反激式设计、我遇到了一些技术问题、希望您能够对此加以说明。

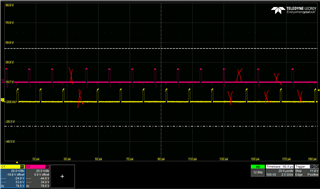

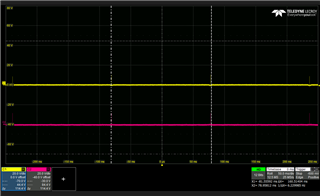

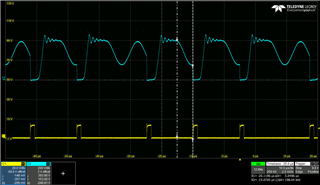

我面临的问题是 OUTPUTA 和 OUTPUTB 在相同负载条件下经常错过周期。 OUTPUT_A 连接到 MOSFET 的栅极、OUTPUT_B 保持开路。 我已经验证过 ILIM 保持在电流限制/过流阈值以下。

通道#1:OUTA |通道#2:OUTB |通道#3:CLK

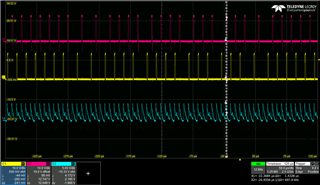

CH1:OUTA、CH3:MOSFET 上的 V_DS

想知道您是否对这个周期跳跃问题/特性有任何建议。 部件/电路的哪个部分可能控制 VDS 上的此谷值检测/多少为零电压开关?