注意:我在这篇文章中提到的元件名称来自 UCC27223的数据表

我正在监控在不断变化的负载和输入电压条件下的 VLO 电压(C2上)。 我所发现的是、在高输出负载和高输入电压条件下、VLO 电压降至3.9V 以下、从而触发了 UVLO 条件。 我已经确认了到引脚3 (VDD)的输入电压没有下降到太低、并且我已经将3个10uF 陶瓷电容器与 UCC27223并联、以使输入电压在负载下保持稳定。

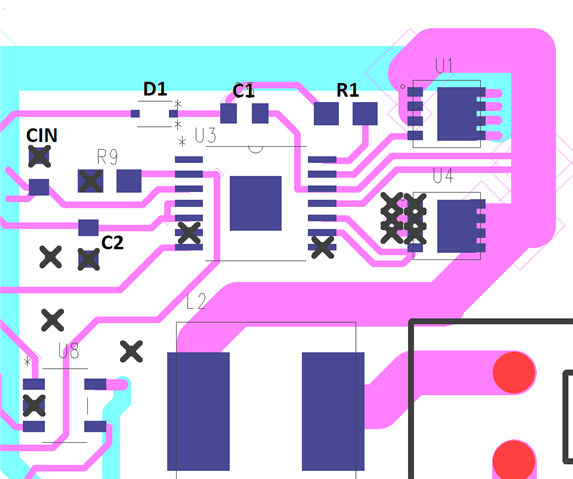

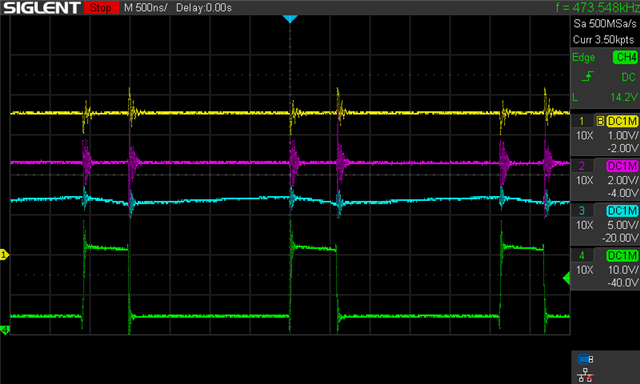

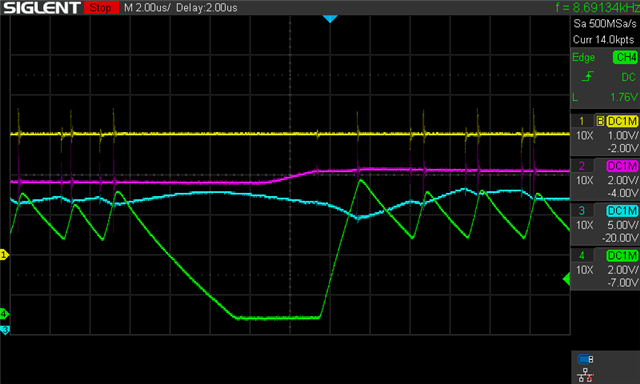

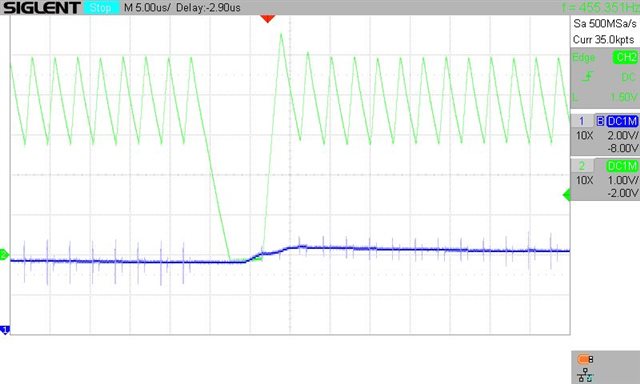

我认为对于 IC 内部的 VLO 生成、我有一件事是不理解的。 下面是正在发生的事情的图片:

CH1 (蓝色) VLO 信号。

CH2 (绿色): 本例中输出电流波形、约为4A RMS

- VLO 有一个慢速衰减,当它下降到大约3.9V 时, UCC 复位。 当没有负载时、VLO 弹回4.2V 左右、且 UCC 重新启动。

我已经对肖特基二极管 D1的不同额定电流(1A 与3A)进行了实验。 这不会产生任何影响。

我已经更改了 VHI 电阻器 R1的值。 0欧姆是最坏的情况-如上图所示、在大约4A RMS 的输出下会发生复位。 当 R1更改为4.7 Ω 时、在发生 UVLO 复位之前、输出电流可以增加到大约6A RMS。 将 R1增大到10欧姆不会提供超过4.7欧姆的任何改善。 为了便于参考、我在下面提供了一个表格、其中显示了我正在试验的各种 FET。 它们都具有相当低/相当相似的栅极电荷规格。

将 C2的值从2x1uF MLCC 降至单个100nF 电容器无疑会使问题更糟:在这种情况下、ULVO 在输出电流约为2A RMS 时触发。

我实验了不同的 C1值、从100nF 到220nF、但这显示的改进很小。

我感到奇怪的是、在给定的输出电流电平下、例如5A RMS、如果以1V 为增量将输入电压从14V 增加到17V、UVLO 复位会变差。 在17Vin 时、负载必须降至3A RMS、以防止触发 UVLO。 如果我将输入电压降低到12V、则可以将输出电流增加到6A RMS、UVLO 不会触发。 当我将其增加到7A 时、UVLO 将开始触发。

UCC27223数据表指出 C2不应超过4.7uF。 此时我需要一些指导、因为我认为问题可能是我将使用的目标 FET 的 C2、C1、R1和 D1值的组合。

供参考:

输入电压:10-17V

PWM 输入来自迟滞驱动电路(输出端是电流源)。 我感应输出电流、将 INA180A2馈送到高速运算放大器、以创建引脚7的 PWM 输入信号。 如果您给我发送一个私人链接、我可以分享原理图。

工作频率约为300-350kHz。 频率随负载和 Vin 而变化。 如果效率有所提高、我会选择更高的频率。

有什么想法?