团队成员

让我来询问 SCP。

检测到 SCP 是高侧 FET 还是低侧 FET 的导通电阻?

我在数据表中找到了"SN0805016使用上部 MOSFET 开关的 RDS (ON)作为电流检测、

但观察该器件的内部电路、首先将 SW/2和 VDD 电压与一个放大器进行比较、用作使能信号、并比较和检测 SW 电压和 ILIM 设置。

如果 SW 电压是 GND 基准、则似乎在比较低侧 FET 电压和设置的 ILIM。

我怎么能理解呢?

此致

达津市

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

团队成员

让我来询问 SCP。

检测到 SCP 是高侧 FET 还是低侧 FET 的导通电阻?

我在数据表中找到了"SN0805016使用上部 MOSFET 开关的 RDS (ON)作为电流检测、

但观察该器件的内部电路、首先将 SW/2和 VDD 电压与一个放大器进行比较、用作使能信号、并比较和检测 SW 电压和 ILIM 设置。

如果 SW 电压是 GND 基准、则似乎在比较低侧 FET 电压和设置的 ILIM。

我怎么能理解呢?

此致

达津市

Chris、您好!

感谢您的答复。

让我再确认一下。

・Ω 的 SW 电压是高侧 FET 两端的电压吗?

・如何测量 SCP 检测点(高侧 FET 电压)?

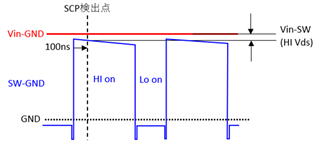

=>在高侧接通100ns 后,测量 VIN-GND 和 SW-GND 之间的差值(高侧 Vds)是否正确?

滤波器衰减?

=>了解检测点处的电压差超过设定阈值(105,180,310mV)并计数7次以触发 SCP 是否正确?

此致

达津市