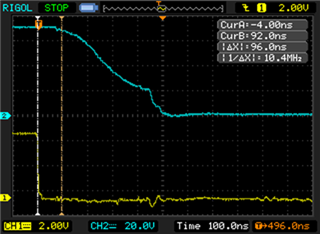

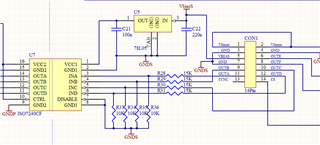

主题中讨论的其他器件: UCC27524、 ISO7240CF、UCC27714、 UCC28950、UCC27714EVM-551

工具与软件:

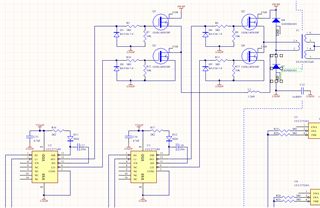

我正在努力推出一款基于 UCC28951的 PSFB 电源设计。 最终目标是在输入电压为60VDC 至200VDC 时达到48VDC @ 90A。 我基于设计的 webench 设计报告随附在我的最终原理图中。

e2e.ti.com/.../WBDesign3-_2800_2_2900_.pdfe2e.ti.com/.../JQ101A_2D00_SchDoc.pdfe2e.ti.com/.../JQ102A_2B00_Mods_2D00_SchDoc.pdf

到目前为止、我一直在尝试让它以60VDC 的输入电压和0至4安培的极轻输出负载运行。 在48VDC 时输出电压正确、但我担心次级上会出现高电压振铃且效率相当低

.

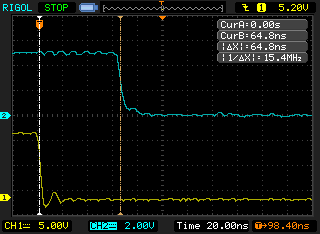

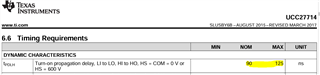

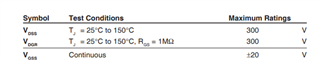

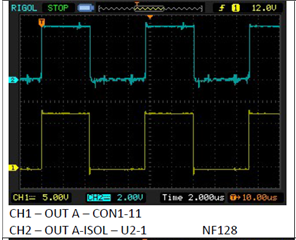

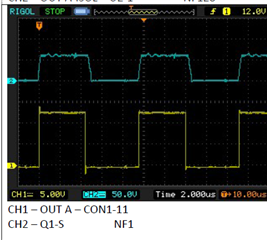

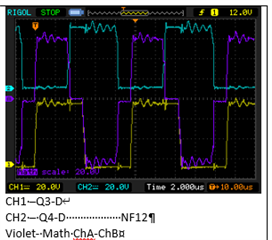

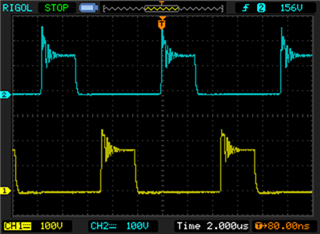

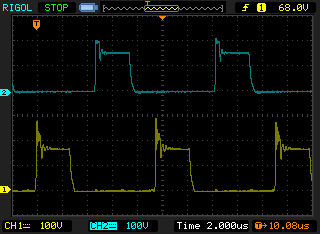

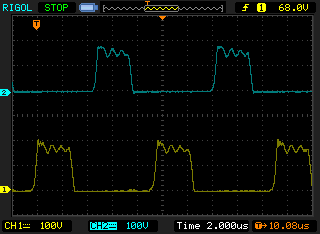

上述示波器屏幕截图为:

CH1 = Q6-D-S、CH2 Q7-D-S (输出 FET)。

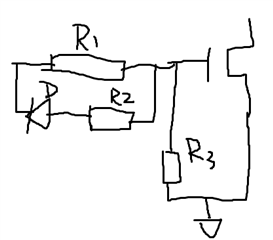

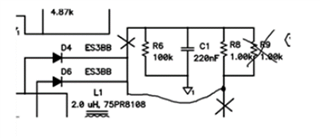

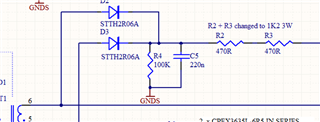

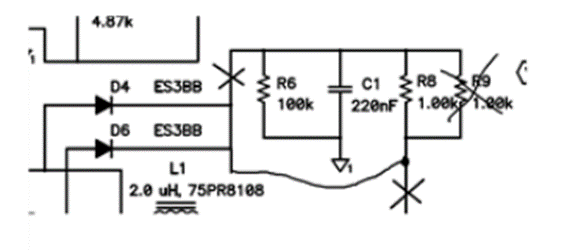

安装了 RCD 缓冲器电路、将 R2-R3电阻器替换为3W 1K2电阻器会在大约30秒后冒烟。

Vin 为60V @ 1.2A (72W)在47R 负载(48.4W)条件下、Vout 为47.7V、效率为67%。

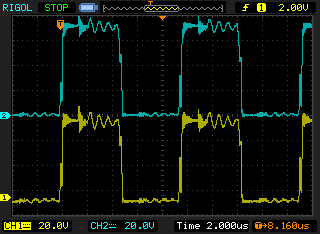

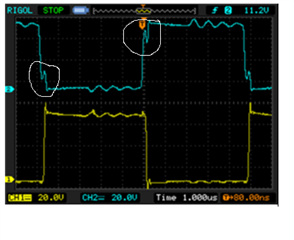

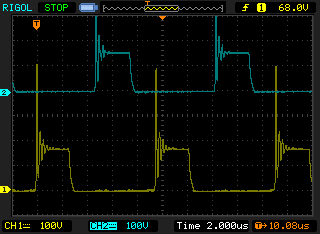

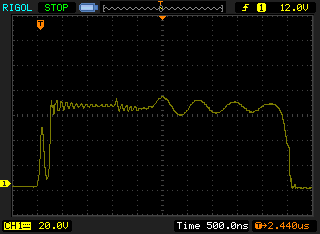

因此、我尝试移除 RCD 缓冲器、我得到了这样的结果:

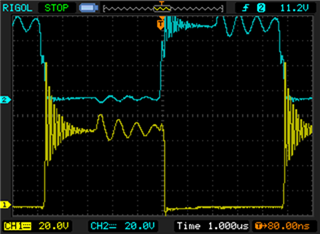

非常高的振铃电压尖峰。 VIN 为60V @ 1.493A (89.6W) Vout 47.7V 47R 负载(48.4W)效率54%。

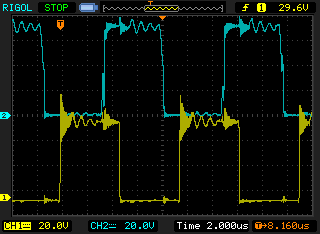

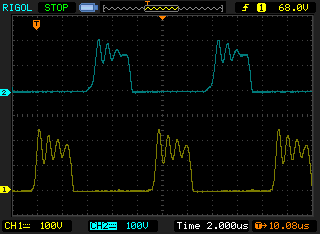

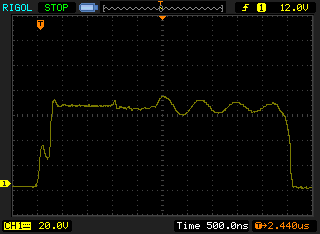

因此、我决定尝试直接在 Q6 Q7 FET D-S 上添加一个 RC 缓冲器 经过多次试错后、我得到了5nF 0R39 RC。

输入电压为60V @ 1.2 (72W)、输出电压47.7V 47R 负载(48.4W)、效率为67%。

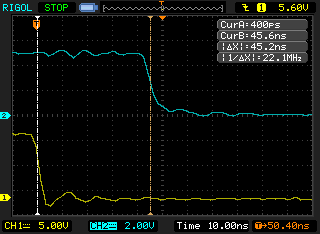

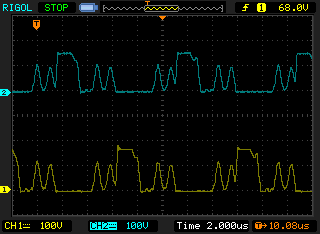

振铃随着负载的增加而增加、如下所示。

输入电压为60V @ 2.4 (144W)输出电压47.7V 23.5负载(96.8W)效率67%。

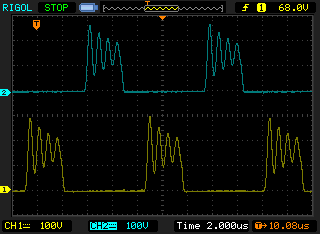

同时安装 RC 缓冲器和 RCD 缓冲器后、振铃得到了更大的改善、但效率会下降、并且 RCD 缓冲器电阻器会升温。

输入电压60V @ 1.424A (85.4W)输出电压47.7V 47R 负载(48.4W)效率57%。

以上所有内容都是在使用10R 电阻器将栅极接地的情况下禁用 Q6、Q7、因为在低功率级别下、同步 FET 不工作、仅使用内部二极管。

作为一项测试、我尝试使用二极管 S3D50065D1替换 Q6、Q7。

IIN 985mA @ 60V (59.1W)输出电压47.7V 47R 负载(48.4W)效率82%。 因此、效率看起来要好很多、但我不确定主脉冲的任一侧都会出现振铃。

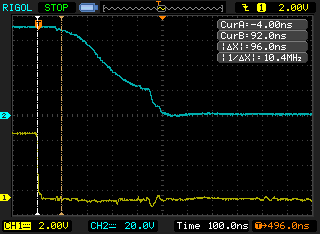

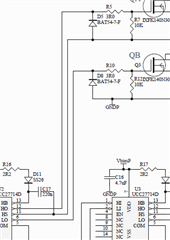

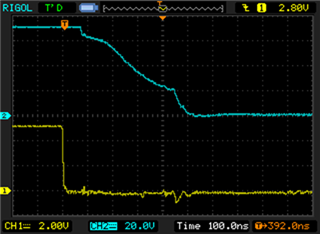

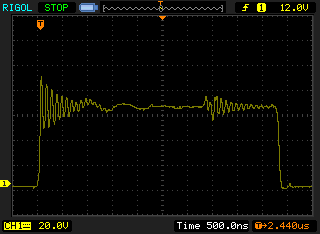

我还在初级 FET Q3和 Q4上产生了振铃。

以上是 Q3上的振铃。 I 使用 D-S 上的5nF 6R RC 缓冲器进行了改进、如下所示。

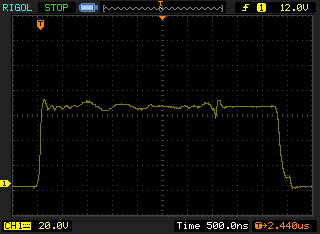

这在 Q4上产生振铃

使用5nF 6R RC 缓冲器进行了改进、如下所示。

那么、我的问题是:

为何会出现这种振铃? 我没有看到其他 UCC28951电路和评估板上使用了 RC 缓冲器。

为什么 Webench 设计和评估板中所示的 RCD 缓冲器会消耗如此大的功率? 在如此低的输出功率下、这是否正常、从而导致轻负载时效率极低?

如何提升此设计的输出功率、不仅是1-4安培、而是大约90安培。 我担心随着功率的增加、情况会变得更糟。 我认为振铃已经导致控制卡产生干扰、并且我在与 Q6和 Q7相连时损坏了许多 UCC27524栅极驱动器。

非常感谢您提供任何建议。 我花费了大量的时间、只是为了达到现在的状态、而且似乎还有很长的路要走才能使其达到全功率。