工具与软件:

您好!

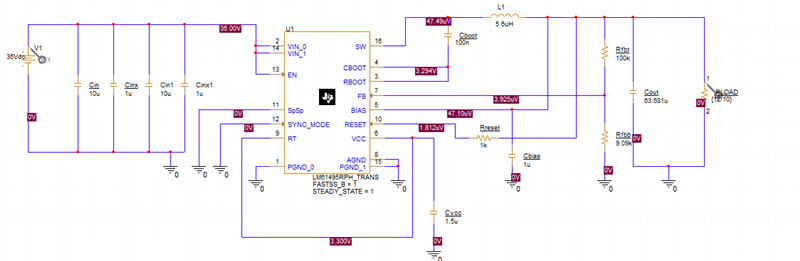

我已经使用 LM61495组件对几个电路进行建模来进行效率测试、但遇到了效率计算超出预期的重复问题。 从仿真结果可以看出、这些设计的目标是在10A 电流下实现12Vout。 不过、在实施平均输入和输出功率布线以计算效率时、即使让仿真运行超过一小时、它们似乎仍在不断收敛、即使没有达到平稳水平、从而导致了高效率结果、这是我所期望的。 此值比 LM61495数据表使用这些电路参数建议的值大、在使用 webench 电源设计工具对新电路建模并在 PSpice for TI 中创建新电路进行仿真后、发生了类似的结果、使效率达到97%以上(此时 webench 计算为96.9%)。 我附上了用于此操作的电路的图片。

此外、每当我尝试通过将 RT 引脚接地以在较低电流配置下调整到2.2MHz 频率时、仿真都显示初始输入电流电平非常大、>25kA、我不知道为什么。 我的方法对于这些错误吗?

谢谢你。