工具与软件:

你好

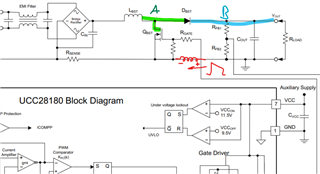

我们将 PFC 驱动器用于 BLDC 电机应用、其输出电压为380V、功率约为1000W。

那么该电路本身就可以正常工作。 但在测试中、PFC 控制器会反复出现故障。 误差始终是相同的 GATE 引脚对 GND 引脚短路。 GATE 引脚上的测量结果表明、关闭时电压介于-0.5..1.5V 之间。

负电压在高负载和空载时最高。

如果我有一个小负载、可能为10%、负电压会更低。

我尝试了以下措施、但没有帮助:

-A -散料二极管与 GATE 引脚和 GND 引脚并联;

-10...100pF 并联至 FET 上的栅极-引脚和源极-引脚。

-2..10kR、与 FET 的栅极和源极并联。

-布局优化

唯一有用的方法是显著减小栅极电阻器(3...5R)。 这里有一个68R。

我们选择68R 来保持低于 EMC 测试的限值。

现在恐怕、如果缩小栅极电阻、EMC 测试将无法通过。

我还可以尝试哪些其他措施?

测量:

蓝色:PFC 控制器的(+)门引脚和(-) GND 引脚

橙色:(+)栅极引脚和(-) FET 的源极引脚

奇怪的是、负电压只在 PFC 上出现、而不在 FET 上出现。 彼此之间的距离约为1.2cm