工具与软件:

嗨、团队:

在应用 TPS1H200A-Q1高侧开关芯片时、我们会遇到通电时触发闭锁的问题。 我们需要与您确认:

1.接通电源时故障诊断的逻辑?

2.当我们尝试将电流限值设置为10A 时、我们发现无法达到该限值。 实际最大值小于3A。 因此、我想问的是、可以设置的电流限制阈值的最大值是多少?

3.我也想确认电流达到电流限值后的计时方法。 如果电流降至一半以下电流限值、然后再次达到电流限值、是否会重新启动时序?

感谢您的支持!

BR、

Ethan

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

嗨、团队:

在应用 TPS1H200A-Q1高侧开关芯片时、我们会遇到通电时触发闭锁的问题。 我们需要与您确认:

1.接通电源时故障诊断的逻辑?

2.当我们尝试将电流限值设置为10A 时、我们发现无法达到该限值。 实际最大值小于3A。 因此、我想问的是、可以设置的电流限制阈值的最大值是多少?

3.我也想确认电流达到电流限值后的计时方法。 如果电流降至一半以下电流限值、然后再次达到电流限值、是否会重新启动时序?

感谢您的支持!

BR、

Ethan

尊敬的 Ethan:

1. DIAG_EN 和 FAULT 引脚是否被拉高? 如果 DIAG_EN 为高电平、则将报告故障。 如果没有故障、则故障电压应为高电平;如果有故障、则故障电压应为低电平。 您还可以参阅 表7-2。 特定情况下的故障真值表。

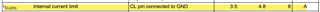

2.这是因为内部电流限值;不能把外部限值设为10A。 外部电流限制必须小于内部电流限制、否则内部限制将接管。

3.您的延迟引脚配置是什么样的? "如果电流降至一半电流限值以下"这句话究竟是什么意思?

谢谢!

Rishika Patel

尊敬的 Rishika:

感谢您的答复。 我将添加一些信息。

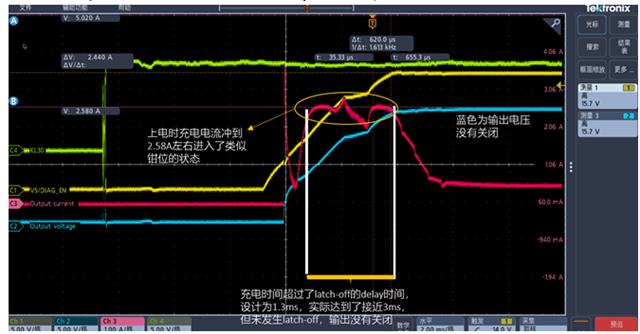

当我们按如下方式配置芯片时(配置1)、会在上电期间发生误触发闭锁保护的问题。 ①前级的15V 可以正常建立、启动时间为15ms;②后级输出建立、大约3.4ms 后停止;

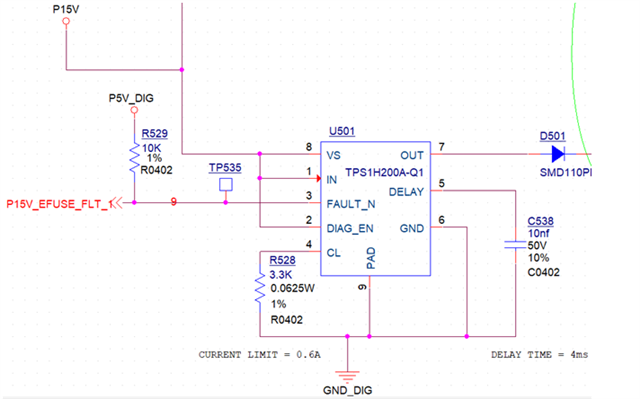

配置1为:

VS 引脚/IN 引脚/DIAG_EN 引脚短路在一起并连接到15V 输入

2. FAULT 引脚通过外部5V 电压上拉。 该5V 电源建立的速度相对较慢、因此故障引脚在上电过程中可能会在一段时间内处于悬空状态

3.3K 电阻下拉 CL 引脚、电流限制配置为0.6A

4.延迟电容设计为10nF、延迟时间设计为4ms

该芯片随后以另一种方式进行配置(配置2)

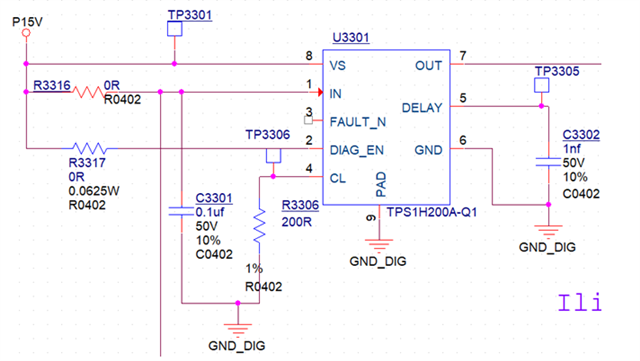

配置2为:

VS 引脚和 DIAG_EN 引脚短接在一起、连接至15V 输入、IN 引脚上拉5V、FAULT 引脚保持悬空

200Ω 电阻下拉 CL 引脚、电流限制配置为10A

3.延迟电容设计为1nF、延迟时间设计为最大1.3ms

在配置2的上电过程中出现以下两个问题:

设计的电流限制为10A、但实际测量的最大值仅为2.6A、小于内部电流限制范围(3.5A、6A)

2.上电电容的充电时间超过1nF 电容设计的1.3ms 延时时间、但输出并未关闭

上一封电子邮件中的问题[我想在电流达到电流限制后确认计时方法。 如果电流降至中间电流限值以下、然后再次达到电流限值、则应确认:

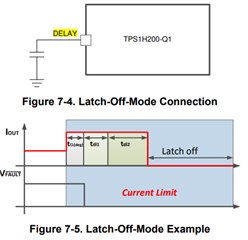

充电电流达到电流限值后会下降、然后再次达到电流限值、与上图中黄圈区域的波形类似、是否会重新计算闭锁延迟时间? 如果该引脚会重新计算、

它可以解释充电时间超过闭锁延迟时间但输出未关闭的现象。

请帮我再看一遍,谢谢~

BR、

Ethan

尊敬的 Ethan:

外部电流限制无法设置为10A、因为内部电流限制的最大值为6A。

如果在延迟时间结束(tdl1 + tdl2)之前移除过流条件、则延迟时间应复位、因为电流未保持在该最大值、而是在波形中下降。 请参阅以下内容。

负载上有什么? 负载类型是什么以及您在该测试期间是否使用了电子负载? 如果是、它是处于恒阻模式还是恒流模式?

谢谢!

Rishika Patel