主题中讨论的其他器件: TPS65994BH

工具与软件:

尊敬的 TI 团队:

正如标题所述、我尝试使用自定义工具来禁用 I2C1和 I2C2的中断屏蔽的所有值、但也失败、但 IO 配置设置 引脚多路复用为 GPIO 和禁用是可以的。 请帮助检查 pjt 文件、谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

尊敬的 TI 团队:

正如标题所述、我尝试使用自定义工具来禁用 I2C1和 I2C2的中断屏蔽的所有值、但也失败、但 IO 配置设置 引脚多路复用为 GPIO 和禁用是可以的。 请帮助检查 pjt 文件、谢谢。

结果:

我使用了所提供的 PJT 和固件、但无法重现结果。

设置:

我使用了他们提供的 PJT 和 FW 基本映像、并将两者加载到了 TPS65994BH EVM 中。 我使用了 Saleae 逻辑分析仪来收集日志并监控器件启动和信号。

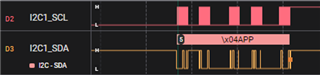

我探测了以下信号:I2C1_IRQ、I2C2_IRQ、LDO_3V3、I2C1_SCL、I2C1_SDA

分析:

我先将 EVM 断电、然后开始进行 Saleae 捕获(已连接)。 然后、我从 VSYS 供电、就像系统并非从 PD 启动一样。

此处 LDO_3V3与 IRQ 信号一起变为高电平。

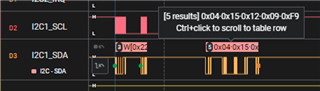

我确认加载了 PJT、因为我在 I2C 日志中看到应用模式:

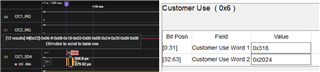

通过读取与 PJT 匹配的客户使用寄存器也可确认:

已确认固件基本映像为 F909.12.15:

在这些读取和测试过程中、IRQ 始终处于高电平。

结论:

这里可能会出现硬件问题、而不是 PD 固件错误。 其他潜在(不太可能)问题可能是因为或存在有效的原因使 I2C1_IRQ 生效、另一个器件将 I2C1_IRQ 拉至低电平(可能是其他 PD 控制器?)、探测到了不正确的信号。

谢谢!

Chris

Michael、

我知道禁用 GPIO 功能会使 GPIO 正常工作。 但是、我无法在具有相同 PJT 和相同基本固件映像的 EVM 上重现此问题。 只有两个不同之处。

如果我的测试序列有问题、请准确详细地告诉我您正在执行的步骤、我可以尝试重新创建。 请告诉我、我还可以做些什么来帮助您调试此问题。

谢谢!

Chris

Chris、您好!

根据我们的测试结果、可以通过设置 PD f/w 来使中断引脚始终处于高电平、因此我们认为它可以通过 PD f/w 来固定、

请帮助检查 PD f/w 设置。

我们对此问题有一些疑问:

1.F/W 设置禁用 I2C1和 I2C2的中断屏蔽的所有值、并且中断状态已清除、为什么中断引脚仍保持低电平?

2.我们知道您的 EVM 上的测试已通过、但我们硬件板上的 PD f/w 禁用 GPIO 引脚也可以正常工作。 因此、将中断引脚保持在低电平不像外部信号或器件那样。

3.我们在 UEFI 模式下测试正常,中断引脚默认值为高,但当系统进入操作系统时,它可能始终保持低电平,并且 f/w 禁用 GPIO 在 UEFI 和操作系统中均通过,我们的测试环境是 Win11 24H2。

4.我们认为禁用 GPIO 和设置 IRQ 并禁用 I2C1和 I2C2的中断屏蔽所有值的 f/w 设置是相同的、因为 f/w 设置不应通知中断、但结果不匹配。

附件是我们硬件 circuit.e2e.ti.com/.../X58_5F00_TI-TBT5-Sch.pdf 的一部分

BR、

Michael

我们重复了此原理图、在 EVM 上看不到相同的行为。 除了外部因素、我们不能回答这个问题。

我们知道您的 EVM 测试通过了、但硬件板上由 PD f/w 禁用 GPIO 引脚的方法也可以正常工作。 因此将中断引脚保持在低电平并不像外部信号或器件那样。[/报价]在我的测试中、我启用了 I2C1_IRQ。 未禁用。

在 UEFI 模式下测试正常、中断引脚默认值为高电平、但当系统进入操作系统时、它可能始终保持低电平那么、如果 OS 关闭(系统关闭)、那么 IRQ 会变为低电平? 那么、这似乎不是 PD 问题。 如果您运行一个简单的测试来打开 PD 控制器的电源并关闭系统的其余部分、如果 IRQ 为高电平、那么它不是 PD 问题。

[报价 userid="626803" url="~/support/power-management-group/power-management/f/power-management-forum/1471021/tps65994ae-tps65994bh-i2c_irq-pin-always-low/5666261 #5666261"]我们认为禁用 GPIO 并设置 IRQ 并禁用 I2C1和 I2C2的中断屏蔽的所有值都是相同的、因为两个 f/w 设置都不应通知中断、但结果不匹配。[/QUOT]错误。 IRQ 是一种备用 GPIO 功能。 禁用所有值时设置的 IRQ GPIO 仍是 IRQ 功能引脚。 已禁用。

谢谢!

Chris

[/quote]