主题中讨论的其他器件: SysConfig

工具与软件:

你(们)好

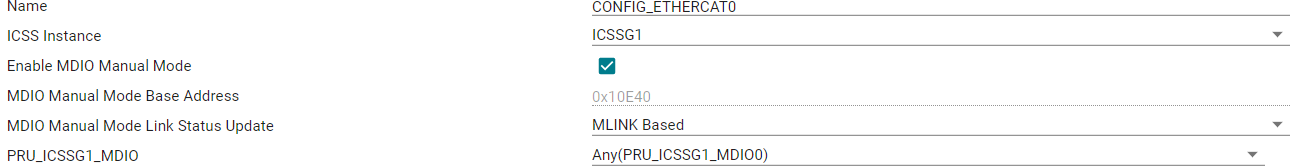

这涉及 EtherCAT 从站-工业协议到基于 AM6421 SOC 的定制电路板的开发/移植。

采取了循序渐进的方法:

- 首先、 使用作为"所用工业通信 SDK:ind_comms_sdk_am64x_09_02_00_15"一部分提供的 EtherCAT 示例 在 带有 Beckhoff PLC 的 AM64x EVM 板上进行测试 这个测试很好、并且能够与 PLC 通信并且将参数发送到 PLC

- 定制电路板具有 AM6421、其中 PHY DP83822具有 MII 配置、PRU 端口与 EVM 电路板中相同。

- PHY DP83822驱动程序配置为 MII、下面提供了寄存器转储。

- 在 EVM 上测试的 EtherCAT 示例已移植到定制电路板。

- 通信失败

在移植过程中完成的操作

- 按照原样使用来自 EVM 的 EEPROM 数据。

- 使用 EVM 中的 PRU 固件原样。

- 使用与现在相同的 EVM 示例应用程序。

需要您的支持、以便向我们提供有关如何建立 EtherCAT 连接的一些线索。

这是 DP83822的寄存器转储

ETHPHY_DP83822_RegDump : Phy[1] Network cable connected PHY 1: BMCR[0] = 0x3100 PHY 1: BMSR[0x1] = 0x7849 PHY 1: PHYIDR1[0x2] = 0x2000 PHY 1: PHYIDR2[0x3] = 0xa240 PHY 1: ANAR[0x4] = 0x01e1 PHY 1: ANLPAR[0x5] = 0x0000 PHY 1: ANER[0x6] = 0x0007 PHY 1: ANPTR[0x7] = 0x2001 PHY 1: ANLNPTR[0x8] = 0x0000 PHY 1: CR1[0x9] = 0x0020 PHY 1: CR2[0xa] = 0x0002 PHY 1: CR3[0xb] = 0x0008 PHY 1: REGCR[0xd] = 0x401f PHY 1: FLDS[0xf] = 0x0000 PHY 1: PHYSTS[0x10] = 0x4015 PHY 1: PHYSCR[0x11] = 0x0108 PHY 1: MISR1[0x12] = 0x6400 PHY 1: MISR2[0x13] = 0x2800 PHY 1: FCSCR[0x14] = 0x0000 PHY 1: RECR[0x15] = 0x0000 PHY 1: BISCR[0x16] = 0x0100 PHY 1: RCSR[0x17] = 0x0241 PHY 1: LEDCR[0x18] = 0x0080 PHY 1: PHYCR[0x19] = 0x8c21 PHY 1: PHYRCR[0x1f] = 0x0241 PHY 1: MLEDCR[0x25] = 0x45e1 PHY 1: GENCFG[0x456] = 0x0008 PHY 1: LEDCFG1[0x460] = 0x0551 PHY 1: SOR1[0x467] = 0x4ec3 PHY 1: LEDCFG2[0x469] = 0x0440 ETHPHY_DP83822_RegDump : Phy[2] PHY 2: BMCR[0] = 0x3100 PHY 2: BMSR[0x1] = 0x7849 PHY 2: PHYIDR1[0x2] = 0x2000 PHY 2: PHYIDR2[0x3] = 0xa240 PHY 2: ANAR[0x4] = 0x01e1 PHY 2: ANLPAR[0x5] = 0x0000 PHY 2: ANER[0x6] = 0x0004 PHY 2: ANPTR[0x7] = 0x2001 PHY 2: ANLNPTR[0x8] = 0x0000 PHY 2: CR1[0x9] = 0x0020 PHY 2: CR2[0xa] = 0x0002 PHY 2: CR3[0xb] = 0x0008 PHY 2: REGCR[0xd] = 0x401f PHY 2: FLDS[0xf] = 0x0000 PHY 2: PHYSTS[0x10] = 0x4002 PHY 2: PHYSCR[0x11] = 0x0108 PHY 2: MISR1[0x12] = 0x0000 PHY 2: MISR2[0x13] = 0x0800 PHY 2: FCSCR[0x14] = 0x0000 PHY 2: RECR[0x15] = 0x0000 PHY 2: BISCR[0x16] = 0x0100 PHY 2: RCSR[0x17] = 0x0241 PHY 2: LEDCR[0x18] = 0x0080 PHY 2: PHYCR[0x19] = 0x8022 PHY 2: PHYRCR[0x1f] = 0x0241 PHY 2: MLEDCR[0x25] = 0x0000 PHY 2: GENCFG[0x456] = 0x0008 PHY 2: LEDCFG1[0x460] = 0x0551 PHY 2: SOR1[0x467] = 0x71c3 PHY 2: LEDCFG2[0x469] = 0x0440