你(们)好

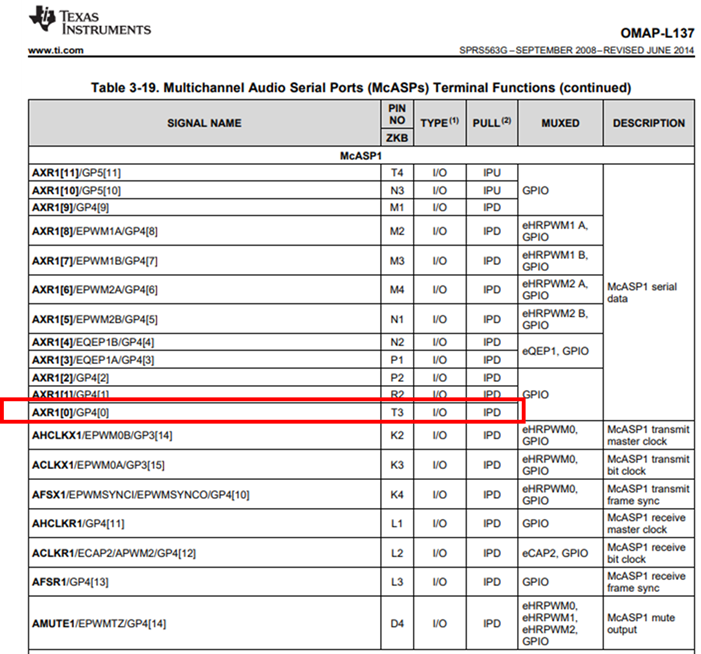

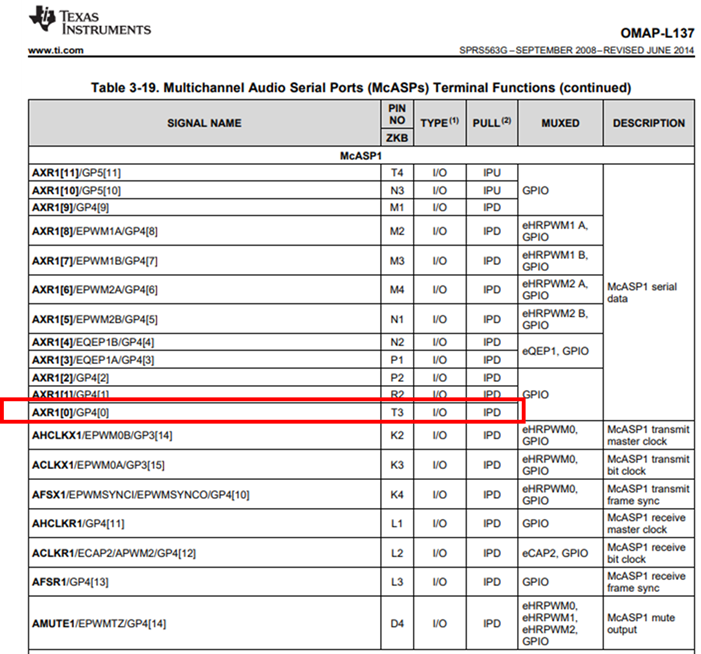

引脚# T3的内部下拉电阻似乎由 HW 启用、但不可通过 SW 配置。

https://www.ti.com/lit/ds/symlink/omap-l137.pdf 表3-19:

10kΩ 使用该信号作为输入、并将其连接到器件外部的3.3V VIE。

10kΩ 不知道该引脚的内部电阻值是多少、恐怕该引脚会随着这些内部下拉电阻和外部 Δ I 上拉电阻而浮动。

请建议如何确认是否正常。

谢谢、此致、

Tsurumoto。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你(们)好

引脚# T3的内部下拉电阻似乎由 HW 启用、但不可通过 SW 配置。

https://www.ti.com/lit/ds/symlink/omap-l137.pdf 表3-19:

10kΩ 使用该信号作为输入、并将其连接到器件外部的3.3V VIE。

10kΩ 不知道该引脚的内部电阻值是多少、恐怕该引脚会随着这些内部下拉电阻和外部 Δ I 上拉电阻而浮动。

请建议如何确认是否正常。

谢谢、此致、

Tsurumoto。

Tsurumoto-San、

在10kO 电阻器上探测时、T3引脚的电压是多少? 在多个电路板上检查它。

如果由于 IPD 争用和外部10k 上拉电阻而导致电压介于 VIL (0.8V)和 VIH (2V)之间、则在器件达到建议的加电小时数之前、这种情况可能会导致可靠性问题。

OMAP-L137数据表中的表5.5指定了"具有相对内部下拉电阻器"条件下的"输入电流"。 该电流加上较小的输入泄漏电流(~35uA)将必须流经外部上拉电阻、这可能导致300uA "最大"电流的显著压降。 但对于50uA 的"最小"电流、我预计电压将高于 VIH (2V)。 如果输入缓冲器上的电压介于 VIL 和 VIH 之间、则输入缓冲器的 PMOS 和 NMOS 区域都部分导通、电流从 VDD 流向 GND、这会在一段时间后导致可靠性问题。 IPD 由晶体管实现、当引脚上的电压达到最高时、晶体管更"导通"。 随着电压下降、IPD 变得更弱。 请参阅 E2E: https://e2e.ti.com/support/processors-group/processors/f/processors-forum/81850/about-internal-pullup-pulldown-resistor-value-of-am3517

对于另一个器件(AM572x SR1.0)、TI 发布了 MMC_DATn 引脚的勘误表、该引脚在复位后启用了 IPD、但需要外部上拉才能进行 MMC 操作。 在该勘误表中、我们解释了在输入的 PMOS/NMOS 部分上通过这两个器件的泄漏电流在3.3V 时每个缓冲器可能会消耗高达2mA 的电流。 对于该器件、我们建议此争用条件在器件生命周期内最多可持续200小时。 我怀疑此器件的建议与此器件类似。 请参阅 SPRZ429M i863 MMC2在从复位释放后立即具有 PU/PD 争用

https://www.ti.com/lit/er/sprz429m/sprz429m.pdf

我们需要联系质量团队、了解该器件能够承受输入缓冲器上的1/2 Vs 电压的最长时间。 并了解潜在损害的延伸。 我将询问是否应将损坏局限于该 IO 单元或更宽泛的单元。

如果这个引脚未被使用、也许它可被启用为一个 GPIO 输出并通过软件驱动一个逻辑高电平(使用 PFUNC 引脚功能寄存器将这个引脚定义为一个 GPIO)。 输出缓冲器的驱动强度将使电压大于 VIH、并消除由于 PMOS/NMOS 在输入缓冲器上都部分导通而导致的泄漏路径。 即使该引脚用作输入、也可以在大部分时间将其配置为输出、并且仅在轮询引脚状态时配置为输入。 这会延迟中电平输入电压引起的可靠性问题。

另请参见 数据表中的4.3上拉/下拉电阻器。 建议使用1K 外部拉电阻器来抵消内部拉电阻器、而20K 建议用作内部拉电阻器的补充。

希望这对您有所帮助、

标记

您好、Mark

感谢您分享上述信息。

>在10kO 电阻器上探测时,T3引脚的电压是多少? 在多个电路板上检查它。

T3引脚作为 GPIO 输入、具有内部下拉和外部10k 上拉电阻。

如果引脚的电压 为

1.827V => GPIO 输入信号被检测为高电平

1.783V => GPIO 输入信号被检测为高电平

1.741V => GPIO 输入信号被检测为高电平

1.725V => GPIO 输入信号被检测为高电平

1.488V => GPIO 输入信号被检测为低电平

1.457V => GPIO 输入信号被检测为低电平

根据上述电压结果、 用于内部下拉的晶体管如何工作?

我还有一个与引脚 T3信号阈值相关的问题。

以下内容是否描述了输入信号的阈值?

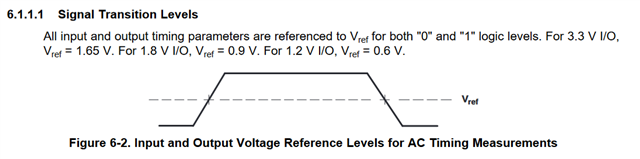

https://www.ti.com/lit/ds/symlink/omap-l137.pdf

如果引脚 T3的电压高于1.65V、那么是否检测到高电平?

此外、如果引脚 T3的电压低于1.65V、那么它是否会被检测为低电平?

谢谢、此致、

Tsurumoto。

您好、Tsurumoto-San、

1.827V 至1.457V 的电压范围介于 VIH (2V)和 VIL (0.8V)之间。 如果这种情况持续一段时间、输入缓冲器可能会损坏。

[引用 userid="74227" URL"~/support/processors-group/processors/f/processors-forum/1010064/omap-l137-how-to-confirm-if-the-value-of-external-pull-is-ok/3737313 #37313"]根据上述电压结果, 用于内部下拉的晶体管如何工作?IPD 晶体管的"强度"似乎与外部10k 上拉电阻器大致相同、从而导致输入电压争用。 IPD 晶体管与外部上拉电阻器作斗争 IPD 尝试下拉输入电压、而外部上拉电阻器尝试上拉电压。

问题:将引脚驱动为输出(逻辑高电平)是否会导致电压大于2V? 我建议软件驱动这个引脚作为一个输出来防止 PMOS 和 NMOS 晶体管在 CMOS 输入缓冲器中被部分"打开"所导致的损坏。

meng gao1 说:如果引脚 T3的电压高于1.65V、那么是否检测到高电平?

此外、如果引脚 T3的电压低于1.65V、那么它是否会被检测为低电平?

[/报价]否、图6-2。 表示数据表时序要求和开关特性是从信号超过 Vref (VDD 的50%)的时间开始测量的、而不是从信号超过 VDD 的10%/90%或 VIL/VIH 阈值等其他时间点测量的。 这仅定义了时序测量。 它未定义电压输入要求。

例如、建立时间、从 AFSX0超过 Vref (VDD 的50%)到 ACLKX0超过 Vref (VDD 的50%)的时间、到 ACLKX0超过 Vref (VDD 的50%)的时间、AFSX0输入到 ACLKX0外部输入的时间都是测量的。 这并不意味着信号在通过 Vref (VDD 的50%)时被锁存为逻辑高电平或低电平-信号必须高于 VIH 或低于 VIL 才能被锁存为高电平或低电平。

如果信号小于 VIL 或大于 VIH、则输入信号被定义为逻辑低电平或逻辑高电平。 这些 VIL/VIH 之间的任何电压都未定义。 在输入电压通过 VIH 和 VIL 之间的区域转换时、还存在迟滞以防止逻辑高电平和逻辑低电平之间切换(输入变化状态)。

请参阅5.3建议运行条件

VIH 高电平输入电压、I/O、3.3V = 2V (最小值)

VIL 低电平输入电压、I/O、3.3V = 0.8V (最大值)

VHYS 输入迟滞= 160mV (标称值)此致、

标记

您好、Mark

非常感谢!

>如果电压介于 VIL (0.8V)和 VIH (2V)之间,原因是 IPD 争用和外部10k 上拉电阻,

>这种情况可能会导致设备在达到建议的开机小时数之前出现可靠性问题。

>我们需要联系质量团队,了解该器件能够承受1/2 Vs 电压的最长时间

>输入缓冲器。 并了解潜在损害的延伸。 我将询问是否应将损坏局限于该 IO 单元或更宽泛的单元。

您是否从质量团队获得了有关 POH 的反馈?

浮动 IO 的数量和浮动周期可能会影响 POH 的假设、 因此我还想分享以下信息。

客户发现另外10个 IO 也处于浮动状态。

一个引脚 T3: 启用内部下拉和外部10k 上拉。 信号始终悬空。

10引脚:启用内部上拉和外部下拉。 器件启动后、该信号将浮动1.3秒。

谢谢、此致、

Tsurumoto。

Tsurumoto-San、

很抱歉耽误您的回答。

QRE 团队指出、在中间轨驱动输入确实会由于 Crowbar 电流(PMOS 和 NMOS 部分导通)而导致可靠性升高的风险。 累积电迁移损坏将与爪形电流一致。

[引用 userid="74227" URL"~/support/processors-group/processors/f/processors-forum/1010064/omap-l137-how-to-confirm-if-the-value-of-external-pull-is-ok/3741828 #3741828"]一个引脚 T3: 启用内部下拉和外部10k 上拉。 信号始终悬空。

10引脚:启用内部上拉和外部下拉。 器件启动后、该信号将浮动1.3秒。

[/报价]他们说,T3故障风险将非常严重。 其他引脚将取决于启动次数和众根电流的累积曝光时间。

为了量化可靠性风险、需要进行冗长的 SPICE 仿真和分析。 这需要 BU 设计团队和计划管理的支持。 客户需要通过适当的渠道上报问题。

此致、

标记

Tsurumoto-San、

这仅仅意味着业务部门需要批准资源、以实现对 POH 和故障率进行量化的工作。

在本设计中、T3引脚始终处于1/2 Vs 电压、因此会因电迁移而受损。 仿真和分析可以告诉我们损坏速度有多快。

对于在器件启动后浮动1.3秒的其他引脚、这取决于器件生命周期内处于此状态的累计时间。 这是电路板复位次数的一个因素(输入处于1/2 Vs 电压、导致电迁移)。

业务部门管理层需要通过某种升级来审批此模拟和分析工作。

此致、

标记